Hello,

We are working on a commercial product in which uses ethernet phy DP83848KSQ from Texas Instruments.

It is interfacing with the internal MAC of MCU over RMII mode for 100Mbps.

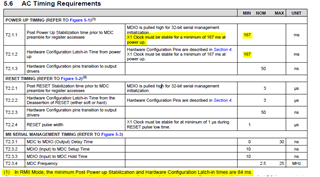

We are looking to verify post power-up stabilization time prior to MDC (PHY datasheet section 5.6 , T2.1.1, pg.no. 11)

As per the PHY datasheet, the minimum post power up stabilization and hardware configuration latch-in times are 84 ms for RMII Mode (Section 5.6, Note 1 in the PHY datasheet) (Please refer image1):

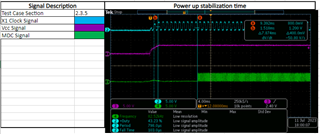

We tested the time requirement on our DUT. The measured value for Post Power up Stabilization is around 7ms - 8ms only which does not meet the recommendation. (Please check image 2)

So we want to know, Is there any impact on ethernet performance? If yes, Please share the problem. How can we resolve the problem to meet our end requirement?

Please let us know if any other information is required.