Other Parts Discussed in Thread: ALP

Hello expert,

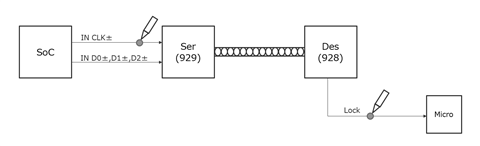

Our customer is facing unexpected tentative black screen issue with DS90UH929/928.

For debugging this phenomena, would you answer following questions?

- Is there any other problem which case lock loss from the view point of 929 and 928 system?

- Channel specification (return loss, insertion loss, cross talk, etc violations)

- HDMI CLK input stability and jitter specifications

- Power supply stability and noise specifications

- Power sequencing issues

- What problem will cause lock loss from DES side?

- Is there any way to confirm the correlation between IN_CLK halting and Lock Loss except directly monitoring IN_CLK and LOCK pin as follows.

- Is there any way to monitor 929's specific bit on 0x0C or 0x5A through GPIO or INTB?

Best regards,

Kazuki Kuramochi