Hi team,

When we tested THVD8000, RS was very easy to be disturbed.

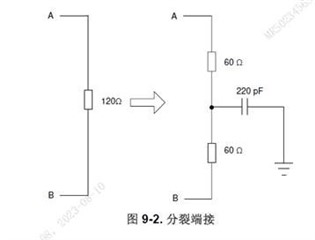

The current configuration is differential mode, the carrier rate is 2M, and the anti-common mode interference design is adopted. In the final test, the bit error rate of RS is 50%, and it is still 20% after adding the magnetic ring.

Questions:

1. What other methods are there to improve the anti-interference ability of this scheme?

2. This product is also used in electric power and building automation. How is the anti-interference design realized?

Thanks!

Rayna