Other Parts Discussed in Thread: ALP

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Sundar,

I will review and get back to you latest by Tuesday Sep, 5th.

Regards,

Fadi A.

Hey Sundar,

If this is an issue with DLP you'd need to submit a ticket under DLP3030 device name to have DLP product line investigate it on e2e.

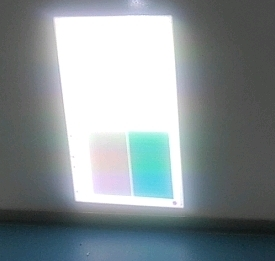

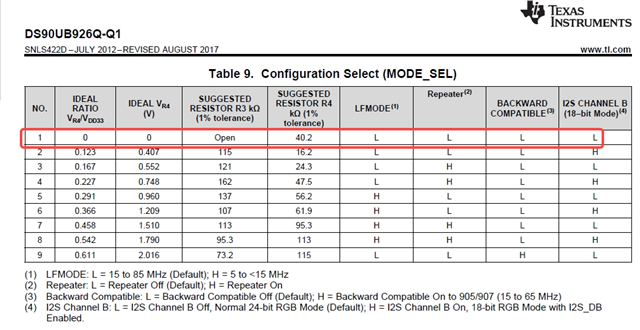

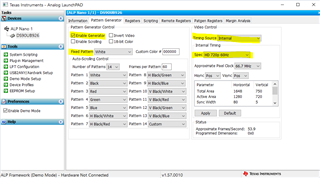

As far as 926 it's pretty straightforward. You can run ALP locally on 926 and generate a test pattern using internal timing to see if you get the correct colors displayed? It's best to test the 926 directly connected to display to rule out DLP3030 issue in the data path.

Initial settings for ALP, choose internal timing to rule out anything from the input side. This way you can test this link: DS90UB926->DLPC120->DLP3030.

Choose your spec resolution and choose internal for timing source and then choose a fixed pattern (Green, red, etc.) and click enable patgen, you should see the same exact pattern on the display.

Regards,

Fadi A.

Hello Fadi,

Thanks for the response.

Sure, we will try the way you suggest.

Also, could you please help find out if the DS90UB926 chip can modify the polarity of the PCLK output signal in software (similar to the rising edge to the falling edge).

Thanks

Sundar

Hey Sundar,

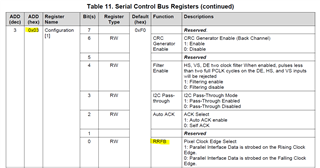

For 926 you can only change the strobe for data on rising or falling clk edge through register 0x03.

Regards,

Fadi A.

Hello Fadi,

Thanks for the response.

Is it possible to share the python script with display timing parameter's for the following setup to load with ALP tool?

941-> 926->DLP3030 (854x480 resolution) (with internal pattern generator of 941 with internal clock and timings - also 941 single mode)

Please help to share this on priority.

Thanks,

Sundar

Hey Sundar,

I will work on this and get back to you within 1-2 business days.

Regards,

Fadi A.

Hey Sundar,

We would need your full timing spec and PCLK to make a script. Please see example script for 960x720 @ 50Mhz PCLK. You can follow this example script to program your timing parameters and PCLK.

import time # timing for each panel is: #960*720@60 #uVisWidth = '960' #uHsyncFrontPorch = '25' #uHsyncWidth = '25' #uHsyncBackPorch = '25' #uVisHeight = '720' #uVsyncFrontPorch = '50' #uVsyncWidth = '50' #uVsyncBackPorch = '50' #uPixelFreqInHz = '50 Mhz Ser_addr = 0x18 time.sleep(0.5) board.WriteI2C(Ser_addr,0x01,0x08) # Reset board.WriteI2C(Ser_addr,0x01,0x02) # Reset time.sleep(0.5) board.WriteI2C(Ser_addr,0x5B,0x1) #Forced STP (Twisted Pair)config and Single FPD-Link III Transmitter mode (Port 1 disabled) board.WriteI2C(Ser_addr,0x1E,0x01) #Select FPD-Link III Port 0 board.WriteI2C(Ser_addr,0x66,0x1A) board.WriteI2C(Ser_addr,0x67,0x01) #M=1 board.WriteI2C(Ser_addr,0x66,0x03) board.WriteI2C(Ser_addr,0x67,0x04) #N=4 -> This is to set the PCLk board.WriteI2C(Ser_addr,0x66,0x04) board.WriteI2C(Ser_addr,0x67,0x0B) #least 8 bit of Total Horizontal frame size board.WriteI2C(Ser_addr,0x66,0x05) board.WriteI2C(Ser_addr,0x67,0x64) #Least 4 bit TV + Most 4 bit TH board.WriteI2C(Ser_addr,0x66,0x06) board.WriteI2C(Ser_addr,0x67,0x36) #Most 8 bit of Total Vertical frame size board.WriteI2C(Ser_addr,0x66,0x07) board.WriteI2C(Ser_addr,0x67,0xC0) #least 8 bit of active Horizontal frame size board.WriteI2C(Ser_addr,0x66,0x08) board.WriteI2C(Ser_addr,0x67,0x03) #Least 4 bit AV + Most 4 bit AH board.WriteI2C(Ser_addr,0x66,0x09) board.WriteI2C(Ser_addr,0x67,0x2D) #Most 8 bit of active Vertical frame size board.WriteI2C(Ser_addr,0x66,0x0A) board.WriteI2C(Ser_addr,0x67,0x19) #Horizontal Sync Width board.WriteI2C(Ser_addr,0x66,0x0B) board.WriteI2C(Ser_addr,0x67,0x32) #Vertical Sync Width board.WriteI2C(Ser_addr,0x66,0x0C) board.WriteI2C(Ser_addr,0x67,0x19) #Horizontal back porch board.WriteI2C(Ser_addr,0x66,0x0D) board.WriteI2C(Ser_addr,0x67,0x32) #Vertical back porch board.WriteI2C(Ser_addr,0x65,0x04) #using internal timing and internal clock board.WriteI2C(Ser_addr,0x64,0x15) #enable Patgen board.WriteI2C(Ser_addr,0x1E,0x01) #Select FPD-Link III Port 0 board.WriteI2C(Ser_addr,0x07,0x58) #0x07,0x58 board.WriteI2C(Ser_addr,0x08,0x5C) #0x08,0x5c board.WriteI2C(Ser_addr,0x03,0x9A) #0x03,0x9A Enable I2C_PASSTHROUGH, FPD-Link III Port 0 board.WriteI2C(Ser_addr,0x01,0x00) #Release DSI

Regards,

Fadi A.

Hello Fadi,

Thanks for the response.

We need it for DLP3030, 854x480 31.5MHZ PCLK.

Please find the below for the display timing paramaters.

Resolution: 854 480

HFP HBP HSYNC:68 72 6

VFP VBP VSYNC:35 9 1

PCLK:31.5

Please help to share.

Thanks,

Sundar

Hey Sundar,

Please see attached with your requested timing. This will run patgen with internal timing/Clk from 941 side.

#This script is generated for an STP system for the following timing

# Resolution: 854 480

#TH = 1000 , TV = 525

# HFP HBP HSYNC:68 72 6

# VFP VBP VSYNC:35 9 1

# PCLK:33.3 Mhz

import time

Ser_addr = 0x18

time.sleep(0.5)

board.WriteI2C(Ser_addr,0x01,0x08) # Reset

board.WriteI2C(Ser_addr,0x01,0x02) # Reset

board.WriteI2C(Ser_addr,0x3,0xDA) #Passthrough I2C

time.sleep(0.5)

board.WriteI2C(Ser_addr,0x5B,0x01) #Force single lane / STP

board.WriteI2C(Ser_addr,0x1E,0x01) #Select FPD-Link III Port 0

board.WriteI2C(Ser_addr,0x66,0x1A)

board.WriteI2C(Ser_addr,0x67,0x01) #M=1

board.WriteI2C(Ser_addr,0x66,0x03)

board.WriteI2C(Ser_addr,0x67,0x06) #N=6

board.WriteI2C(Ser_addr,0x66,0x04)

board.WriteI2C(Ser_addr,0x67,0xE8) #least 8 bit of Total Horizontal frame size

board.WriteI2C(Ser_addr,0x66,0x05)

board.WriteI2C(Ser_addr,0x67,0xD3) #Least 4 bit TV + Most 4 bit TH

board.WriteI2C(Ser_addr,0x66,0x06)

board.WriteI2C(Ser_addr,0x67,0x20) #Most 8 bit of Total Vertical frame size

board.WriteI2C(Ser_addr,0x66,0x07)

board.WriteI2C(Ser_addr,0x67,0x56) #least 8 bit of active Horizontal frame size

board.WriteI2C(Ser_addr,0x66,0x08)

board.WriteI2C(Ser_addr,0x67,0x03) #Least 4 bit AV + Most 4 bit AH

board.WriteI2C(Ser_addr,0x66,0x09)

board.WriteI2C(Ser_addr,0x67,0x1E) #Most 8 bit of active Vertical frame size

board.WriteI2C(Ser_addr,0x66,0x0A)

board.WriteI2C(Ser_addr,0x67,0x06) #Horizontal Sync Width

board.WriteI2C(Ser_addr,0x66,0x0B)

board.WriteI2C(Ser_addr,0x67,0x01) #Vertical Sync Width

board.WriteI2C(Ser_addr,0x66,0x0C)

board.WriteI2C(Ser_addr,0x67,0x48) #Horizontal back porch

board.WriteI2C(Ser_addr,0x66,0x0D)

board.WriteI2C(Ser_addr,0x67,0x09) #Vertical back porch

board.WriteI2C(Ser_addr,0x65,0x04) #using internal timing and internal clock

board.WriteI2C(Ser_addr,0x64,0x15) #enable PG/color bars

board.WriteI2C(Ser_addr,0x1E,0x01) #Select FPD-Link III Port 0

board.WriteI2C(Ser_addr,0x07,0x58) #0x07,0x58

board.WriteI2C(Ser_addr,0x08,0x5C) #0x08,0x5c

board.WriteI2C(Ser_addr,0x03,0x9A) #0x03,0x9A Enable I2C_PASSTHROUGH, FPD-Link III Port 0

board.WriteI2C(Ser_addr,0x01,0x00) #Release DSI

Regards,

Fadi A.