Hi team,

My customer has met a green screen problem when using four 933 pairing with 962.

They send us the reg dump of normal status and abnormal status.

I see there is a difference in 0x35, so I doubt that there is something wrong with their camera. Thus I asked them to change other cameras to check if the problem follows camera. The result is that the problem follows 962.

Then I found the configuration of frame synchronization is not right, then I asked them to change. It works but not totally works: Before changes, the problem exists until power-down and power-up. After changes, the problem disappears itself in a few seconds. So it seems like there is still something wrong in the register setting. Can you have a check on it? I give the reg dump after changes below.

Then I checked their register configuration, I don't see any fault in their config. Pls have a check.

Then they told me they have another project, which uses the same schematic as this one. The only difference is that they use 26MHz crystal in this project, while they use 25MHz crystal in another project. The 25MHz crystal suits well with the system, but the 26MHz crystal has green screen problem.

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef 00: 60 00 1e 40 d0 01 00 fe 1c 10 7a 7a 0f 09 00 ff `.?@??.???zz??.. 10: 00 00 00 00 00 00 00 00 01 06 83 06 83 00 04 02 ........?????.?? 20: 00 3c 04 00 00 00 00 00 00 00 00 00 00 00 00 00 .<?............. 30: 00 00 01 01 00 00 00 0f 00 00 00 00 00 00 00 00 ..??...?........ 40: 00 a9 71 01 00 00 20 00 00 00 00 12 38 c3 55 36 .?q?.. ....?8?U6 50: ff 00 00 00 00 00 00 00 58 00 00 b0 b6 00 00 00 ........X..??... 60: 00 00 00 00 00 00 00 00 00 00 00 00 00 7f 8a 88 .............??? 70: 1e ec e4 03 c0 0a 00 c5 00 01 00 00 c0 00 00 00 ??????.?.?..?... 80: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ 90: 08 00 07 58 ff ff ff ff 00 00 00 00 00 00 00 00 ?.?X............ a0: 00 00 00 00 00 09 00 00 00 00 00 00 00 00 00 00 .....?.......... b0: 1c 3a 15 08 25 00 18 00 8f 3f 83 74 80 00 00 00 ?:??%.?.???t?... c0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ d0: 00 43 94 02 60 f2 00 02 00 00 00 10 00 00 00 00 .C??`?.?...?.... e0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ f0: 5f 55 42 39 36 30 00 00 00 00 00 00 00 00 00 00 _UB960..........

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef 00: 60 00 1e 40 d0 01 00 fe 1c 10 7a 7a 0f 09 00 ff `.?@??.???zz??.. 10: 00 00 00 00 00 00 00 00 01 06 83 06 83 00 04 02 ........?????.?? 20: 00 3c 05 00 00 00 00 00 00 00 00 00 00 00 00 00 .<?............. 30: 00 00 01 01 00 03 00 0f 00 00 00 00 00 00 00 00 ..??.?.?........ 40: 00 a9 71 01 00 00 20 00 00 00 00 12 38 c3 55 2e .?q?.. ....?8?U. 50: 9b 00 00 00 00 00 00 00 58 00 00 b0 b6 00 00 00 ?.......X..??... 60: 00 00 00 00 00 00 00 00 00 00 00 00 00 7f 8a 88 .............??? 70: 1e ec e4 03 c0 0a 00 c5 00 01 00 00 c0 00 00 00 ??????.?.?..?... 80: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ 90: 13 58 12 e4 ff ff ff ff 00 00 00 00 00 00 00 00 ?X??............ a0: 00 00 00 00 00 1d 00 00 00 00 00 00 00 00 00 00 .....?.......... b0: 1c 3a 15 08 25 00 18 00 8f 3f 83 74 80 00 00 00 ?:??%.?.???t?... c0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ d0: 00 43 94 02 60 f2 00 02 00 00 00 00 00 00 00 00 .C??`?.?........ e0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ f0: 5f 55 42 39 36 30 00 00 00 00 00 00 00 00 00 00 _UB960..........

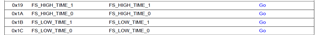

addr 0x30, reg 01 val 01 addr 0x30, reg 19 val 06 addr 0x30, reg 1a val c5 addr 0x30, reg 1b val 06 addr 0x30, reg 1c val c5 addr 0x30, reg 1f val 02 addr 0x30, reg 20 val f0 addr 0x30, reg 4c val 01 addr 0x30, reg 58 val 58 addr 0x30, reg 5c val b0 addr 0x30, reg 6d val 7f addr 0x30, reg 6e val 8a addr 0x30, reg 70 val 1e addr 0x30, reg 72 val e4 addr 0x30, reg 7c val c0 addr 0x30, reg 4c val 02 addr 0x30, reg 58 val 58 addr 0x30, reg 5c val b2 addr 0x30, reg 6d val 7f addr 0x30, reg 6e val 8a addr 0x30, reg 70 val 1e addr 0x30, reg 72 val e4 addr 0x30, reg 7c val c0 addr 0x30, reg 4c val 04 addr 0x30, reg 58 val 58 addr 0x30, reg 5c val b4 addr 0x30, reg 6d val 7f addr 0x30, reg 6e val 8a addr 0x30, reg 70 val 1e addr 0x30, reg 72 val e4 addr 0x30, reg 7c val c0 addr 0x30, reg 4c val 08 addr 0x30, reg 58 val 58 addr 0x30, reg 5c val b6 addr 0x30, reg 6d val 7f addr 0x30, reg 6e val 8a addr 0x30, reg 70 val 1e addr 0x30, reg 72 val e4 addr 0x30, reg 7c val c0 addr 0x30, reg 18 val 01 addr 0x30, reg 21 val 3c addr 0x30, reg 32 val 01 addr 0x30, reg 33 val 01 addr 0x30, reg b9 val 3f addr 0x30, reg 4c val 01 addr 0x30, reg 4c val 12 addr 0x30, reg 4c val 24 addr 0x30, reg 4c val 38 addr 0x30, reg 20 val 00

Questions:

1. Is there any fault on their register configuration?

2. Is there any fault on their schematic?

3. What should we do and test in next step?

Since this project is in mass production status, my customer is under great pressure. Pls give me the answer asap. Thanks for your support.

Regards,

Peter