Part Number: TLK10232

Hello,

We have used TLK10232 dual phy component for a XAUI to SFP/SFP+ application.

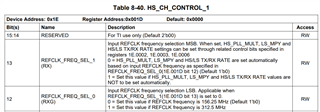

I have a question regarding the value of HS SERDES multiplier setting (Reg 0x1e.0x0002.[3:0])

We operate the chip at REFCLK frequency set to 156.25MHz.

According to HS PLL Multiplier Control Table when this frequency is used the PLL multiplier factor should be 16.5x (value 1100b) but we erroneously use the value 1101b (default) that corrensponds to 20x.

Trying both values seems to have no real impact to phy operation.

How this can be explained?

Note that Auto-Negotiation & Link Training are disabled.

Thanks on advance,

Panayotis