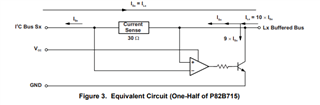

Other Parts Discussed in Thread: , TM4C129ENCPDT, P82B715

I am writing to PCF8574 and PCF8574A devices using the TI driver under TIRTOS.

TM4C129ENCPDT processor, latest TIRTOS available for this processor is being used.

The writes are always working, but the callback does not always return true.

If I write a 1 to bit 0 of the IO expanders, I always get true returned.

However, if I write a 0 to bit 0, some devices will always return with a FALSE state from the driver.

Some devices basically fail every time, others intermittent.

The write itself always works and the outputs are correctly activated but the ACK is not detected and hence the TI driver returns a non successful transfer.

As I wish to be able to detect when the chip is present this causes an issue as I cannot detect the difference between a missing chip or chip not responding because bit 0 is 0.

I noticed someone else reported a similar issue in stack overflow, but no solution was offered.

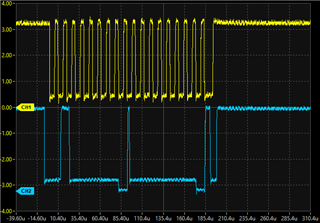

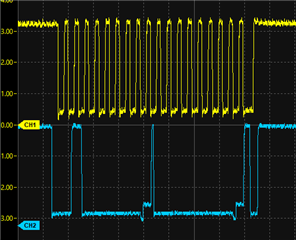

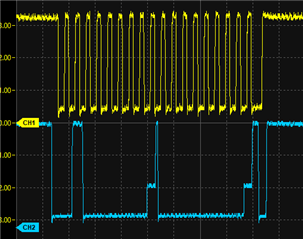

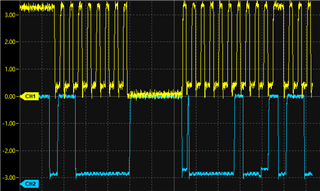

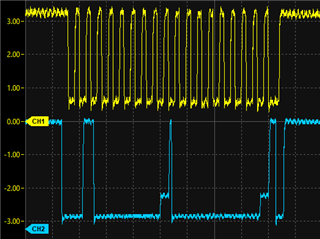

Looking on a CRO it looks like there is an ack but it is delayed sometimes when bit 0 is 0, it is very consistent when bit 0 is 1.

Is there any adjustment that can be made to the driver to allow for a longer delay for the ACK, or is this fixed in hardware.

Issue occurs at both 100kHz or 400kHz so is not speed of the I2C bus related.