- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi all,

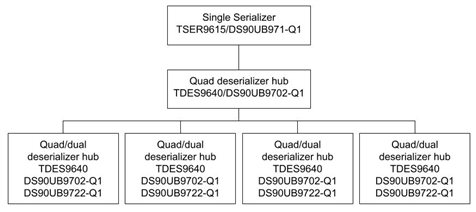

I'm working on a project where I need to distribute a single MIPI CSI stream to four different destinations. I'm considering using a TDES9640/DS90UB9722-Q1, but I'm unsure if it can internally route a single CML input to all the four CML outputs, essentially acting as a fan-out buffer.

Also, Can a single serializer (TSER4915/DS90UB971-Q1) effectively control 5 deserializers (1 act as fan out buffer + 4 at the end points) and maintain bidirectional communication channels?

Regards,

Anin

Hello Anin,

This kind of configuration is not possible since the CMLOUT signal is tied 1:1 with the RX port. You can not assign the CMLOUT ports to all output from one single RX input like this. Also CMLOUT does not have any back channel. It is unidirectional forward channel signal only

Best Regards,

Casey

Thanks for clarifying. Just to confirm, per your statement, no back channel exists between daisy-chained TDES9640/DS90UB9722-Q1.

Assuming different requirements from display serdes like touch and control, does TDES4940/DS90UB984 offer back channel between 2 deserializers connected in daisy chain topology?

Additionally, the mention of 2 clock lanes per MIPI port on TDES9640/DS90UB9722-Q1; does this allow configuring the 2 ports as 4 ports with 1 clock lane and 2 data lanes each?

Anin

Anin,

"Daisy Chain" and "CMLOUT" features are distinct (not the same) within the FPD-Link portfolio. CMLOUT has no back channel, but daisy chain does have full back channel. So TDES4940 for example does support I2C communication and GPIO passthrough across multiple daisy chain hops in either upstream or downstream direction.

Additionally, the mention of 2 clock lanes per MIPI port on TDES9640/DS90UB9722-Q1; does this allow configuring the 2 ports as 4 ports with 1 clock lane and 2 data lanes each?

Yes this is correct. It is possible to configure this through I2C

Best Regards,

Casey