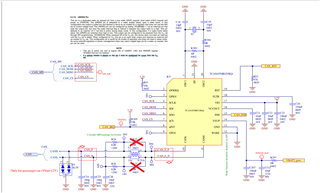

Other Parts Discussed in Thread: TCAN4550

Hello,

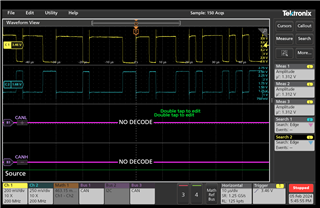

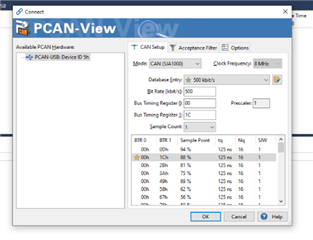

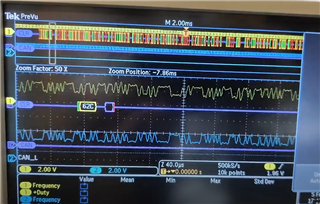

I'm currently working on configuring the CAN bus using the TCAN4550-Q1 CAN controller with SPI interface on an Ambarella platform. While I've been able to establish the can0 network interface and confirm loopback functionality using canutilitis, I'm encountering issues when attempting to trace messages using tools like CANoe or PCAN. I can observe waveform data on the CAN wires using an MSO

root@-:~# ip -details link show can0

2: can0: <NOARP,UP,LOWER_UP,ECHO> mtu 16 qdisc pfifo_fast state UP mode DEFAULT group default qlen 10

link/can promiscuity 0 minmtu 0 maxmtu 0

can state ERROR-ACTIVE (berr-counter tx 0 rx 0) restart-ms 0

bitrate 800000 sample-point 0.800

tq 25 prop-seg 19 phase-seg1 20 phase-seg2 10 sjw 1

m_can: tseg1 2..256 tseg2 2..128 sjw 1..128 brp 1..512 brp-inc 1

m_can: dtseg1 1..32 dtseg2 1..16 dsjw 1..16 dbrp 1..32 dbrp-inc 1

clock 40000000 numtxqueues 1 numrxqueues 1 gso_max_size 65536 gso_max_segs 65535

I am encountering challenges with transmitting messages from the target device. TCAN4x5x controller is successfully receiving data from both PCAN and CanOe.

I am encountering challenges with transmitting messages from the target device. TCAN4x5x controller is successfully receiving data from both PCAN and CanOe.