Part Number: DP83869HM

Other Parts Discussed in Thread: AM6442, DP83869

Hi all,

I asked this question a week ago, but only now realize I don't understand the accepted answer.

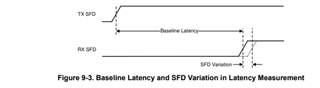

We are looking to use DP86839's GPIO_0 and GPIO_1 pins for 1588 hardware timestamping of TX and RX SFD. To do this we are configuring GPIO_0 using 0x1E0[3:0] = 0x6 = Receive SFD, and GPIO_1 using 0x1E0[7:4] = 0x5 = Transmit SFD. Our timestamp device (AM6442 CPTS) requires a minimum 98ns pulse width.

Q1. Can the SFD pulses on GPIO_0 and GPIO_1 be extended to ensure they are >98ns wide?

Q2. In the previously linked answer, I was told to use 0x1E0[7:4] to adjust SFD pulse timing in 8ns increments. But the datasheet shows 0x1E0[7:4] is for GPIO_1_CTRL. Was this a mistake? Is there another register to adjust the pulse timing for TX/RX SFD on GPIO_0 and _1?