Hi Team,

I have few questions would like to check with you.

1. According to the content, "Each RX port signal path continuously monitors cable characteristics for long-term cable aging and temperature changes." Does it mean that our AEQ change the setting in real time?

2. For the BIST, if our PASS is 'hi' when run BIST. Does it mean that the SerDes link is ok, but we can't guarantee the FPD-Link when transmit the video timing, is it correct? I asked because we have one case that PASS is high when ran BIST, but when we do real data transmission, the lock was unstable and cause the image output flicker.

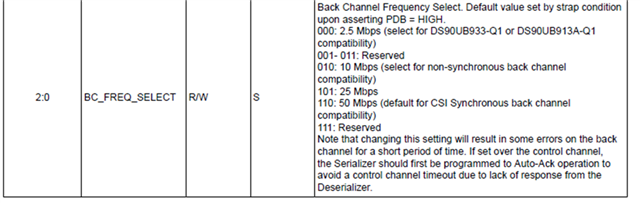

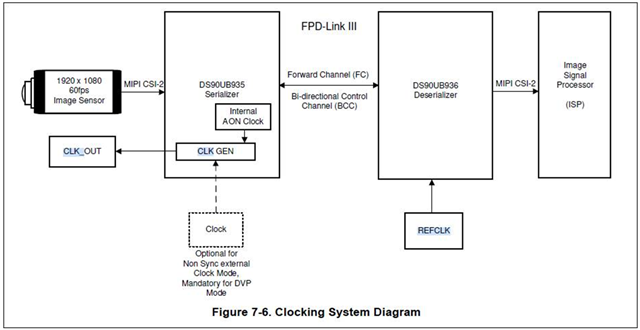

3. When I set the BC_FREQ_SELECT from b101 to b110, the CLK_OUT becomes to 48MHz from 24MHz. Also, the eye width I measured on the Deserializer becomes to 0.25ns from 0.5ns. I'm not sure how to explain the behavior, may you help explain for me?

Regards,

Roy