Part Number: TMDS181

Other Parts Discussed in Thread: SN65DP159,

HI TI Team:

My name is Wesley!

please help me confirm TMDS181 & SN65DP159 schematic?

if any concern Please let me know.

Thank you a lot ^^

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hey Wesley,

Unfortunately, I am only able to get to the schematic review for U3. This was done under the assumption that this is for a sink application.

TMDS181_Schematic _Review_Wesley_(2-22-2024).pdf

I also have a few additional comments:

Who is the OEM/ODM for this project, and what is the project name?

current setup is in pin-strap mode but no DDC snooping, could be a problem.

Make sure CMC is within bandwidth of the HDMI signal used

Make sure clamping voltage for ESD is ~5V

Why are the differential signals being pulled up to 3.3V?

Also for a reference schematic in a sink side application please have a look on page 43 of the TMDS181 Datasheet: https://www.ti.com/lit/ds/symlink/tmds181.pdf?ts=1708620111469&ref_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FTMDS181

I will finish up the review for the U9 and U6 circuits tomorrow and get those to you.

Hi Vishesh:

Who is the OEM/ODM for this project, and what is the project name?-->ODM --> VEGA-3006

current setup is in pin-strap mode but no DDC snooping, could be a problem.

Make sure CMC is within bandwidth of the HDMI signal used-->

Please explain again, I don't understand what you mean.

We currently have other projects to set PIN Strap. From FPGA Team feedback is have DDC Snooping.

At the same time in the 4K source, it is verified PASS !

Make sure clamping voltage for ESD is ~5V-->

Please explain the component number ?

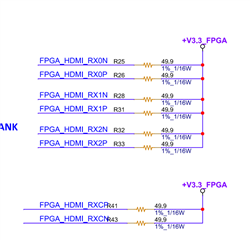

Why are the differential signals being pulled up to 3.3V?

-->Because the TMDS181 output is connected to FPGA, FPGA does not have the internal Pull Hi 3.3V Pin Type.Need external Pull Hi

Please refer to TMDS181 DS Page15

PS: SCH NL/ is no mount.

Thank you^^

We currently have other projects to set PIN Strap. From FPGA Team feedback is have DDC Snooping.

At the same time in the 4K source, it is verified PASS !

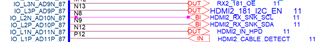

Just wanted to make sure snooping was being done as I cant see the DDC connection to the FPGA.

Make sure CMC is within bandwidth of the HDMI signal used-->

I cant see the part number for the common mode choke(CMC) you are using, so I want to make sure that the CMC is good enough for HDMI 2.0 bandwidth. Here is a chart with many CMCs that should work for your application:

Make sure clamping voltage for ESD is ~5V-->

I looked into the part and it should be fine.

-->Because the TMDS181 output is connected to FPGA, FPGA does not have the internal Pull Hi 3.3V Pin Type.Need external Pull Hi

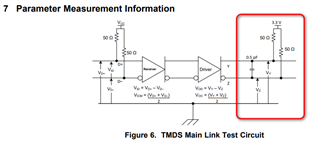

Please refer to TMDS181 DS Page15

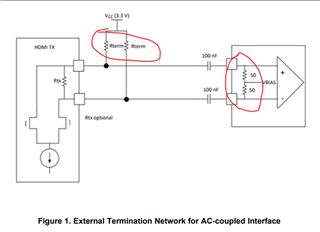

This circuitry was for parameter measurement, not for application use. This is the schematic for an AC coupled application. In practice they should be the same, but just for future reference.

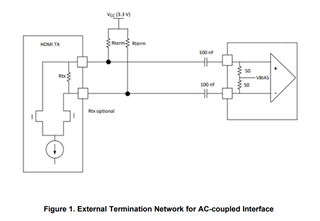

AC coupled implementation:

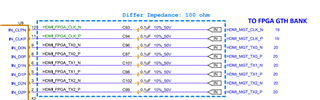

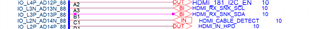

I didn't see the AC coupling circuitry at the bottom on the schematic, apologies. However, it seems there is a naming mismatch for the HDMI TX1 Clock.

The circuitry for U6 looks like its the same as U3, so all of the above should apply to U6 as well. Working on the U9 schematic review.

Here are some additional points I missed in my first run over the schematic review.

Hi Vishesh:

Just wanted to make sure snooping was being done as I cant see the DDC connection to the FPGA.

-->please view RX1 U4 & RX2 U7 & TX U10 is from DDC connection to the FPGA. I have confirmed from FPGA.

2.I cant see the part number for the common mode choke(CMC) you are using, so I want to make sure that the CMC is good enough for HDMI 2.0 bandwidth. Here is a chart with many CMCs that should work for your application:

--->Our Si simulation team recommends that the HDMI 2.0 RX side does not use CMC,So we only use CMC on the HDMI 2.0 TX side.

3.This circuitry was for parameter measurement, not for application use. This is the schematic for an AC coupled application. In practice they should be the same, but just for future reference.

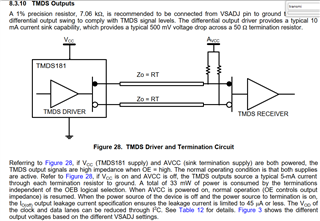

-->Because TMDS 181 transmission end DC terminal

, Must be on the terminal Pull Hi 49.9 OHM to 3.3V. We used to try to remove the terminal Pull Hi 49.9 OHM to 3.3V. FPGA will not be able to receive it

Information from TMDS181.

Anyway, the DP159 is AC signal transmission at the TX end, so it does not need to be like TMDS181 on the terminal Pull Hi 49.9 OHM to 3.3V.

4.I didn't see the AC coupling circuitry at the bottom on the schematic, apologies. However, it seems there is a naming mismatch for the HDMI TX1 Clock.

--->The HDMI TX end must have a lookback function, so the TX FPGA side Ref CLK will come from CLK_GEN

5.The circuitry for U6 looks like its the same as U3, so all of the above should apply to U6 as well. Working on the U9 schematic review.

-->YES!

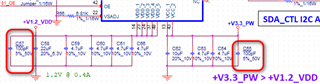

I modify the RX1 & RX2 & TX1 power supply high -frequency wave capacitance

RX1 & RX2 & TX1 new add 100pF CAP

Hey wesley,

Thanks so much for the quick feedback and communication. Let me know how the discussions with the FPGA team goes. I will look into the DDC pullup values.

Hi Vishesh:

Thank you for your quick reply^^

I confer with FPGA Team as shown below:

Hey Wesley,

On the TMDS181, 40.2k pullup on DDC_SDA/SCL is out of HDMI spec, need use 47k +/-10%-->we refence Xilinx EVB is set 40.2K OHM

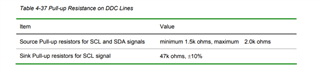

As per the HDMI spec you need to have a 47k ohm resistor on the DDC lines:

We cannot see what Xilinx is doing internally at these pins, so please consult with them and confirm that they are meeting spec with their reference design.

- Between TMDS181 & FPGA, the characteristics of using AC capacitance isolation DC. We don't think there will be a condition of Create Double Termination. Thank you^^

You will still need to math the terminations between the FPGA and the the output to reduce reflections. Tuning may need to be done based off of the internal terminations of the FPGA

FPGA input requires to be AC coupled, but TMDS181 output needs to be 3.3V common mode voltage, so use external 50ohm termination to 3.3V to set the CM. But 50ohm termination and FGPA input termination create double termination so output signal amplitude gets cut in offer. May need to adjust TMDS181 output SWING to compensate-->we circuit TMDS181 TMDS 49.9OHM Pull up 3.3V--> AC CAP ---> input FPGA MGT BANK.

The text is referring to figure 1 above:

If possible it may be best to use DC coupled HDMI signaling to simplify the system and reduce the number of caps needed the BOM.

Hey Wesley,

Based off the information provided, it seems that the double termination, and the DDC pull ups have been addressed. Let me know if you need anything else from our end.

HI Vishesh

Thank you very much for your detailed confirmation .

Please turn off this issue.

Thank you a lot^^