Part Number: DS125DF111

Other Parts Discussed in Thread: DS125DF1610, DS100MB203, DS250DF230, USB2ANY, , DS125MB203

Hello Team,

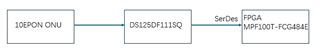

At present, the optical module ONU is directly connected to the SerDes interface of the FPGA,

but the optical sensitivity can only be measured to -31.5dBm (unqualified), and the optical sensitivity is required to reach -33dBm.

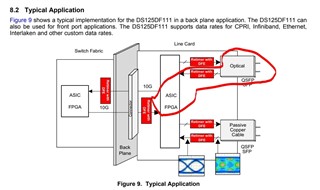

I want to use DS125DF111SQ, but I don't know if I can use it, what should I pay attention to?

FPGA model: MPF100T-FCG484E, in fact, the FPGA cannot catch the error of 10E-3 , and the system needs to be shaped by the retimer chip.

Thank you!