Part Number: SN65DSI83

Hi TI experts,

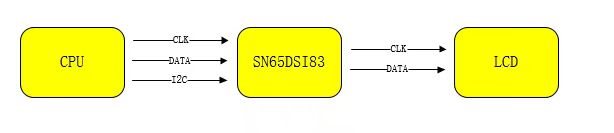

We want to use SN65DSI83 between CPU and LCD display as below:

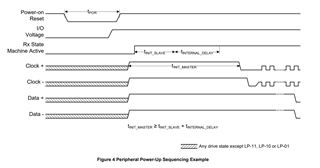

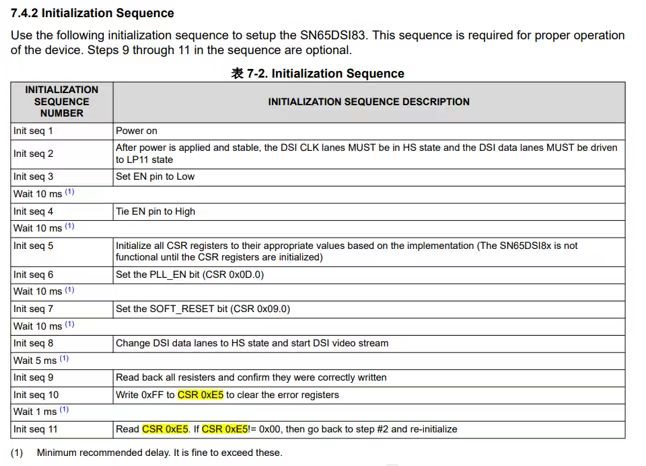

Now we configured according to the steps in the data sheet, but in the second step, the DSI data must be driven to LP11 state (that is, setting the data to high level) was limited by the underlying driver of the CPU. We could only let The data is kept output, and then the following series of resets, register configuration, PLL enable and other operations are performed. But in the end, the internal PLL of SN65DSI83 could not be locked.

if there is a way to solve this situation.