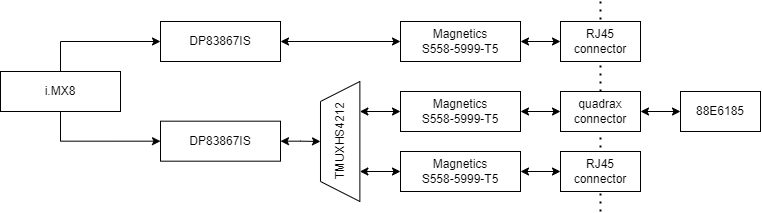

Part Number: DP83867IS

Hi

We are using DP83867IS in 100M mode and are having a hard time getting the link stable. RX_CTRL pin is strapped to mode 3 (autoneg disable = 0), but noticed that the infamous bit 7 of register 0x0031 (INT_TST_MODE_1) is set. We also noticed that bit 8 of 0x006F is set, indicating test mode entry from RX_CTRL's strap is not requested (datasheet p76: If RX_CTRL is strapped to mode1/mode2 then PHY will go to

internal test mode. Reg x6F[8] = 0 will also indicate the test mode entry request from RX_CTRL's strap.)

Clearing bit 7 of 0x0031 does not result in stable link.

What can explain this behavior, and how can we get a stable link?

Best regards