Hi,

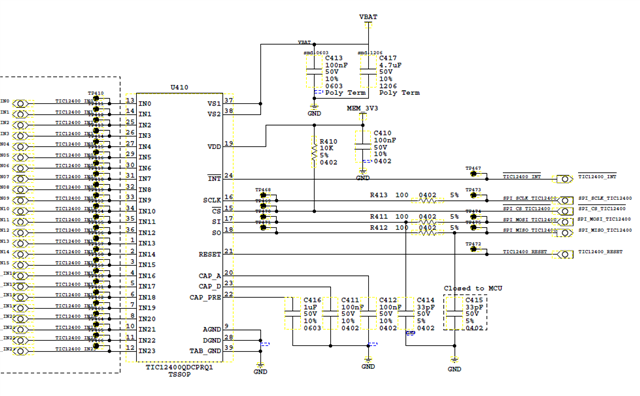

I configured the TIC12400 but eventhough the level on the INx is changed from 11V to 0V (switch to GND), there is NO SSC interrupt generated.

When switch x switches to GND, the current will go up x * the wetting current

INx all configured as CSO

WC_CFG0,WC_CFG1 2mA or 10mA (only above current will increase)

IN_EN all enabled

INT_EN_COMP1, INT_EN_COMP2 all set to 3 (falling and rising edge)

INT_EN_CFG0 All interrupts are enabled

CONFIG = 0x7E18E8 (continous mode)

Mode all zero.

POR, CALC_CRC, UV interrupt can be received when doing SW reset / init / low voltage

Any idea why it doesn't work?

Thanks,

Paul