Other Parts Discussed in Thread: TCAN4550

Hi,

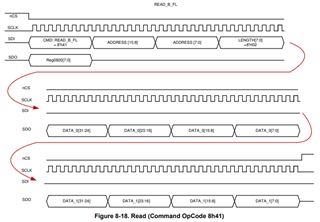

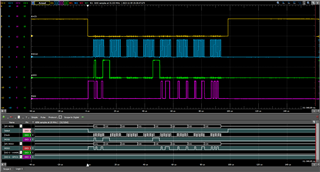

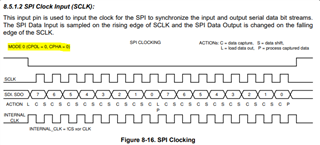

Continuing from the linked question. I tried to check if there is any issue with the SPI on the Linux board I was using. I did not find any issue there. Have got Logic Analyzers and tried capturing those waveforms. Here is the link to the waveforms. I see that MISO is always LOW. I am not sure if this is expected. There is some data on MOSI.

Thanks,

Sai Kiran.