Other Parts Discussed in Thread: TCAN4550,

Hello,

we are trting to setup tcan4550 under spi on our embedded linux 6.1

we mange to see the SPI line is sending clock on boot - but can't get the tcan to work

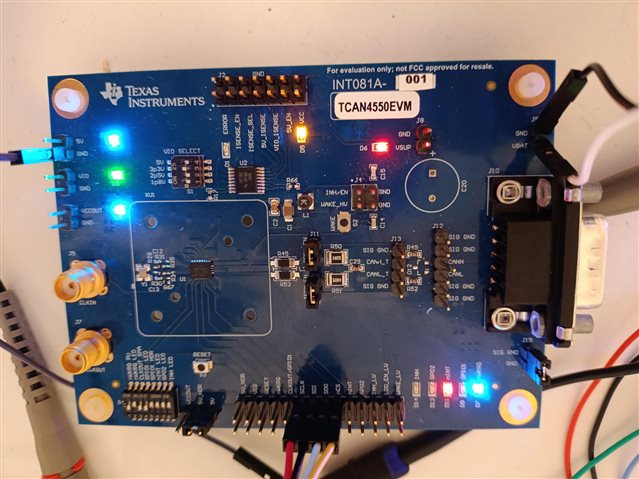

right now we are using the tcan4550evm board - connecting spi to spi

and PIN16 to VBAT to power on the device

this is the device tree we are using :

spi1: spi@fc000000 { //using PA16 for poweron tcan on spi1

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_spi1_default>;

clocks = <&pmc PMC_TYPE_PERIPHERAL 34>;

clock-names = "spi_clk";

status = "okay";

// spidev@0 {

// compatible = "spidev";

// reg = <0>;

// spi-max-frequency = <100000>;

// #address-cells = <1>;

// #size-cells = <1>;

//};

tcan: can@0 {

//Device_Tree: https://docs.zephyrproject.org/latest/build/dts/api/bindings/can/ti,tcan4x5x.html

//Driver: https://git.kernel.org/pub/scm/linux/kernel/git/torvalds/linux.git/tree/drivers/net/can/m_can

//example: https://stackoverflow.com/questions/41828308/reading-writing-spi-devices

compatible = "ti,tcan4x5x";

reg = <0>;

#address-cells = <1>;

#size-cells = <1>;

spi-max-frequency = <1000000>;

// clocks = <&main_xtal>;

clock-frequency = <20000000>;

clocks = <&pmc PMC_TYPE_PERIPHERAL 34>;

clock-names = "spi_clk";

// clock-names = "spi_clk";

// device-state-gpios = <&pioA PIN_PA16 GPIO_ACTIVE_HIGH>;

// device-wake-gpios = <&gpio0 1 GPIO_ACTIVE_HIGH>;

// reset-gpios = <&gpio0 2 GPIO_ACTIVE_HIGH>;

int-gpios = <&pioA PIN_PC5 GPIO_ACTIVE_HIGH>;

// bosch,mram-cfg = <0x0 15 15 5 5 0 10 10>;

bosch,mram-cfg = <0x0 0 0 16 0 0 1 1>;

bus-speed = <250000>;

bus-speed-data = <1000000>;

status = "disabled";

// can-transceiver {

// max-bitrate = <8000000>;

// };

};

};

on demseg we get this:

dmesg | grep spi

atmel_spi fc000000.spi: Using dma0chan0 (tx) and dma0chan1 (rx) for DMA transfers

atmel_spi fc000000.spi: Using FIFO (16 data)

atmel_spi fc000000.spi: registered master spi3

spi spi3.0: setup: bpw 8 mode 0x0 -> csr0 0000000a

spi spi3.0: DEactivate NPCS, mr 000f0031

spi spi3.0: setup mode 0, 8 bits/w, 1000000 Hz max --> 0

atmel_spi fc000000.spi: registered child spi3.0

atmel_spi fc000000.spi: Atmel SPI Controller version 0x311 at 0xfc000000 (irq 153)

tcan4x5x spi3.0: no clock found

tcan4x5x spi3.0: no CAN clock source defined

tcan4x5x spi3.0: setup: bpw 8 mode 0x0 -> csr0 0000000a

tcan4x5x spi3.0: DEactivate NPCS, mr 000f0031

tcan4x5x spi3.0: setup mode 0, 8 bits/w, 1000000 Hz max --> 0

tcan4x5x spi3.0: activate NPCS, mr 000e0031

atmel_spi fc000000.spi: start fifo xfer (ptrval): len 8 tx (ptrval) rx (ptrval) bitpw 8

tcan4x5x spi3.0: DEactivate NPCS, mr 000f0031

tcan4x5x spi3.0: activate NPCS, mr 000e0031

atmel_spi fc000000.spi: start fifo xfer (ptrval): len 8 tx (ptrval) rx (ptrval) bitpw 8

tcan4x5x spi3.0: DEactivate NPCS, mr 000f0031

tcan4x5x spi3.0: activate NPCS, mr 000e0031

atmel_spi fc000000.spi: start fifo xfer (ptrval): len 8 tx (ptrval) rx (ptrval) bitpw 8

tcan4x5x spi3.0: DEactivate NPCS, mr 000f0031

tcan4x5x spi3.0: activate NPCS, mr 000e0031

atmel_spi fc000000.spi: start fifo xfer (ptrval): len 8 tx (ptrval) rx (ptrval) bitpw 8

tcan4x5x spi3.0: DEactivate NPCS, mr 000f0031

tcan4x5x spi3.0: activate NPCS, mr 000e0031

atmel_spi fc000000.spi: start fifo xfer (ptrval): len 8 tx (ptrval) rx (ptrval) bitpw 8

tcan4x5x spi3.0: DEactivate NPCS, mr 000f0031

tcan4x5x spi3.0: activate NPCS, mr 000e0031

atmel_spi fc000000.spi: start fifo xfer (ptrval): len 8 tx (ptrval) rx (ptrval) bitpw 8

tcan4x5x spi3.0: DEactivate NPCS, mr 000f0031

tcan4x5x spi3.0: activate NPCS, mr 000e0031

atmel_spi fc000000.spi: start fifo xfer (ptrval): len 8 tx (ptrval) rx (ptrval) bitpw 8

tcan4x5x spi3.0: DEactivate NPCS, mr 000f0031

tcan4x5x spi3.0: activate NPCS, mr 000e0031

atmel_spi fc000000.spi: start fifo xfer (ptrval): len 8 tx (ptrval) rx (ptrval) bitpw 8

tcan4x5x spi3.0: DEactivate NPCS, mr 000f0031

tcan4x5x spi3.0: activate NPCS, mr 000e0031

atmel_spi fc000000.spi: start fifo xfer (ptrval): len 8 tx (ptrval) rx (ptrval) bitpw 8

tcan4x5x spi3.0: DEactivate NPCS, mr 000f0031

tcan4x5x spi3.0: Unsupported version number: 0

tcan4x5x: probe of spi3.0 failed with error -22

can someone point out what is missing? and what is the problem ?

or where to search for the problem ?

Thank you ,