Part Number: DP83822I

Tool/software:

Hi Team,

We have interfaced PHY DP83822IRHBT to the NXP controller MIMXRT1176CVM8A in RMII Master mode configuration.

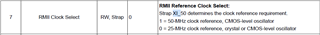

We have connected the Boot strap pins of PHY as per below table.

| Boot strap pins | Connected in Schematics as below | Pull up/Pull down connected |

| COL | NC since RMII master mode | No |

| RX_D0 | Controller's MAC's Receive pin | No |

| RX_D1 | Controller's MAC's Receive pin | No |

| RX_D2 | NC since RMII master mode | No |

| RX_D3 | NC since RMII master mode | No |

| LED_0 | Connected to LINK LED of LAN Connector | No |

| LED_1 | Connected to SPEED LED of LAN Connector | No |

| CRS | Controller's MAC's CRS pin | No |

| RX_ER | NC since RMII master mode | No |

| RX_DV | Controller's MAC's DV pin. | No |

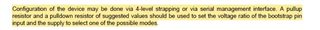

In Section 8.5.1 of PHY datasheet it is mentioned as below:

My question is:

As per the above image, configuration of PHY can be done via Serial management interface and we are planning to use this option instead of 4-level hardware boot strapping. In this case, are the connections of the boot strap pins as per the above table, acceptable?