Part Number: DP83TC814S-Q1

Other Parts Discussed in Thread: DP83TC812EVM-MC

Tool/software:

Hello TI Team,

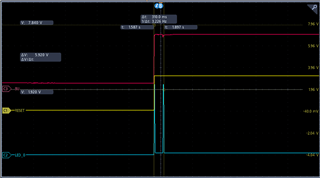

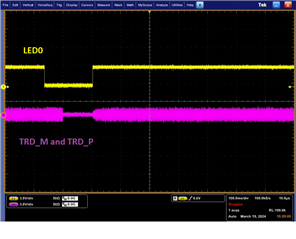

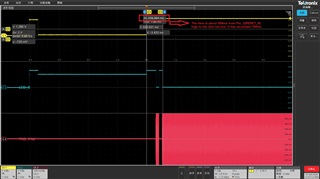

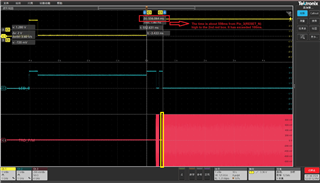

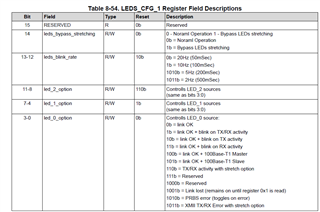

LED0 has the function of Link-OK indication.

Does it output blink_rate when it links OK?

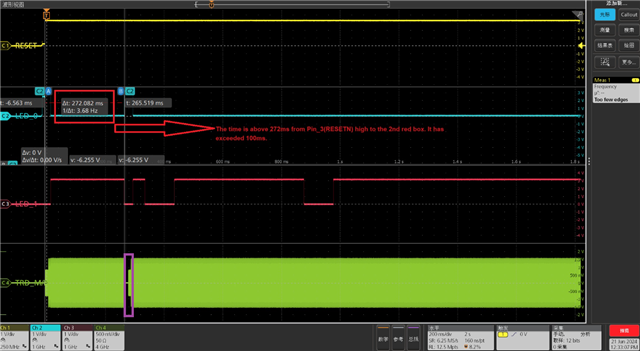

Now, we can't measure the blink rate when it links ok.

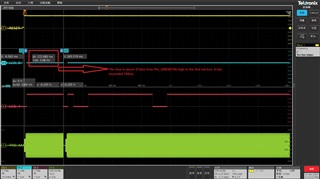

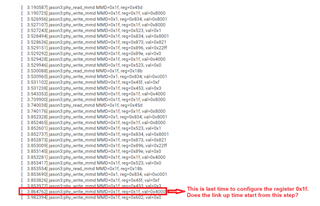

How to configurate the function?

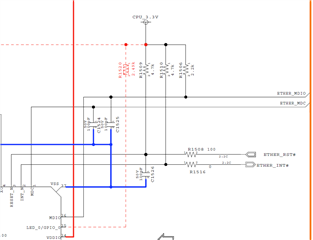

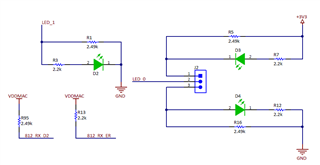

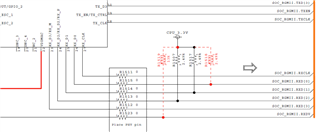

Below is our schematic:

Best Regards!