Part Number: DS90UB933-Q1

Tool/software:

Hi HPD Link team,

I have some questions about DS90UB933-Q1 application, I'll be grateful to get your reply~

1.The UB913, UB913A, and the UB933 are all pin-to-pin compatible, I wonder if they can be used as a direct replacement in an existing design when set 10bit mode, I mean using same PCB, same software and same components, just solder different Ser devices;

2. For UB933-UB934 application, I think they support BT.656 8-bit and BT.601 16-bit, do they support BT.1120?

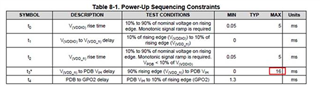

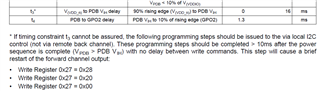

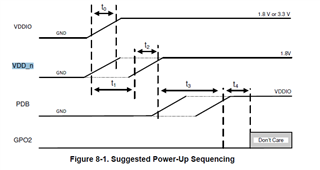

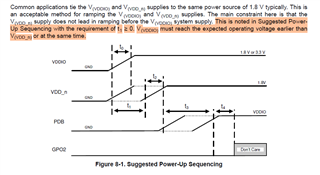

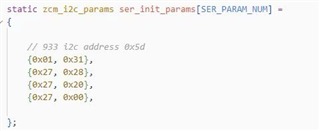

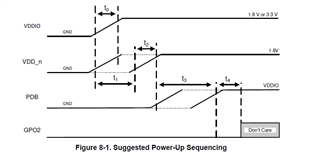

3. My customer system power up sequence doesn't meet with the requirement of datasheet, VDD_n power up before VDDIO, here is their initial code, please check if it's OK:

Besides, do we have other ways to initial if the power up sequence doesn't meet with the requirement of datasheet?

4. For SOC-UB933-UB962 application, if SOC output wrong data to UB933, is there a register to indicate this error?

Looking forward to your kindly reply, thanks~

Best Regards,

Jack