Part Number: DP83867IS

Tool/software:

Hi,

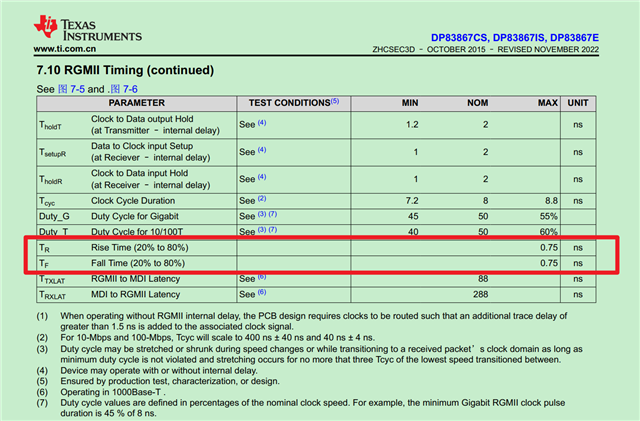

Question 1: DP83867ISRGZ uses RGMII for connection, what is the rise and fall time of the output RX-CLK signal?

Question 2: Find a parameter in the manual as shown in the following figure, but it is not specified whether it is an input parameter for TXCLK or an output parameter for RXCLK.

Question 3:

The MAC used by the customer requires an input clock rise and fall time of 0.54ns. Is there any way to adjust the rise and fall time of the DP83867 output clock signal?

Thanks!