Tool/software:

The process we handle is:

Tool/software:

The process we handle is:

Hello Li,

I will test this and get back to you as soon as possible.

Regards,

Anagha

Hello Li,

I tested this issue internally as well as by following the steps you listed above, and was unable to recreate it. I am using the DP83TC813R-Q1 with the DP83TC812 as a link partner.

Would you mind sharing what your current setup is?

Regards,

Anagha

0x834 = 0xc001

0x523 = 0x0001

0x81C = 0x0fe2

0x872 = 0x0300

0x879 = 0x0f00

0x806 = 0x2952

0x807 = 0x3361

0x808 = 0x3D7B

0x83E = 0x045F

0x834 = 0x8000

0x862 = 0x00E8

0x896 = 0x32CB

0x03E = 0x0009

0x01f = 0x4000

0x523 = 0x0000

Would you mind sharing what your current setup is?

All register values in our testing environment:

reg:0x0 value:0x2100

reg:0x1 value:0x61

reg:0x2 value:0x2000

reg:0x3 value:0xa211

reg:0x10 value:0x4

reg:0x11 value:0x10b

reg:0x12 value:0x4000

reg:0x13 value:0x0

reg:0x15 value:0x0

reg:0x16 value:0x100

reg:0x17 value:0x0

reg:0x18 value:0x5a25

reg:0x19 value:0x808

reg:0x1B value:0x0

reg:0x1E value:0x0

reg:0x1F value:0x0

reg:0x41 value:0x88f7

reg:0x133 value:0x5e0

reg:0x17F value:0x4028

reg:0x180 value:0x0

reg:0x181 value:0x0

reg:0x182 value:0x0

reg:0x183 value:0x0

reg:0x184 value:0x203

reg:0x185 value:0xa

reg:0x187 value:0x100

reg:0x188 value:0x80

reg:0x189 value:0x40

reg:0x18A value:0x40

reg:0x18C value:0x0

reg:0x18E value:0x8004

reg:0x300 value:0x2710

reg:0x301 value:0x1703

reg:0x302 value:0x45

reg:0x303 value:0x419

reg:0x304 value:0x30

reg:0x305 value:0x4

reg:0x306 value:0xa

reg:0x310 value:0x0

reg:0x430 value:0x770

reg:0x450 value:0x2600

reg:0x451 value:0x1

reg:0x452 value:0x100

reg:0x453 value:0x6

reg:0x456 value:0x0

reg:0x457 value:0x6483

reg:0x458 value:0x1

reg:0x45D value:0x31c8

reg:0x45F value:0x3

reg:0x485 value:0x1078

reg:0x486 value:0xa05

reg:0x489 value:0x1

reg:0x496 value:0x44c

reg:0x497 value:0x1c0

reg:0x4A0 value:0x1000

reg:0x553 value:0x0

reg:0x560 value:0x7e4

reg:0x561 value:0x0

reg:0x562 value:0xfb

reg:0x600 value:0x38

reg:0x601 value:0x0

reg:0x602 value:0x3

reg:0x603 value:0x0

reg:0x608 value:0x7b

reg:0x609 value:0x0

reg:0x60A value:0x323

reg:0x60B value:0x5

reg:0x60C value:0x24

reg:0x60D value:0x0

reg:0x618 value:0x0

reg:0x619 value:0x574

reg:0x61A value:0x5dc

reg:0x61B value:0x7d

reg:0x61C value:0x0

reg:0x61D value:0x0

reg:0x61E value:0x0

reg:0x620 value:0x0

reg:0x622 value:0x0

reg:0x623 value:0x0

reg:0x624 value:0x5511

reg:0x625 value:0x0

reg:0x626 value:0x0

reg:0x627 value:0x0

reg:0x628 value:0x0

reg:0x629 value:0x0

reg:0x62A value:0x0

reg:0x639 value:0xa

reg:0x63A value:0x0

reg:0x63B value:0x0

reg:0x63C value:0x0

reg:0x63D value:0x0

reg:0x63E value:0x0

reg:0x648 value:0x120

reg:0x649 value:0x0

reg:0x64A value:0x10

reg:0x871 value:0x0

reg:0x1000 value:0x2100

reg:0x1001 value:0x61

reg:0x1007 value:0x2001

reg:0x100B value:0x0

reg:0x1012 value:0x0

reg:0x1834 value:0x8000

reg:0x1836 value:0x5008

reg:0x3000 value:0x2100

reg:0x3001 value:0x61

Hello Li,

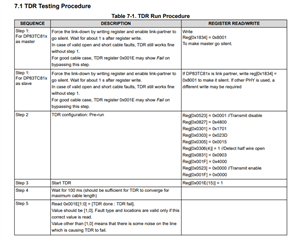

Feel free to follow the TDR test procedure described under section 7 of the following app note: https://www.ti.com/lit/an/snla389b/snla389b.pdf?ts=1721068514278&ref_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FDP83TC812R-Q1

Additionally, these are all of the register values from our testing environment:

Register 0000 is: 2100

Register 0001 is: 0061

Register 0002 is: 2000

Register 0003 is: a211

Register 0010 is: 0004

Register 0011 is: 010b

Register 0012 is: e400

Register 0013 is: 0000

Register 0015 is: 0000

Register 0016 is: 0100

Register 0017 is: 0000

Register 0018 is: 5a25

Register 0019 is: 080a

Register 001B is: 0000

Register 001E is: 0000

Register 001F is: 0000

Register 0041 is: 88f7

Register 0133 is: 05e0

Register 017F is: 4028

Register 0180 is: 0000

Register 0181 is: 0000

Register 0182 is: 0000

Register 0183 is: 0000

Register 0184 is: 0203

Register 0185 is: 000a

Register 0187 is: 0100

Register 0188 is: 0080

Register 0189 is: 0040

Register 018A is: 0040

Register 018C is: 0000

Register 018E is: 8004

Register 0300 is: 2710

Register 0301 is: 1703

Register 0302 is: 0045

Register 0303 is: 0419

Register 0304 is: 0030

Register 0305 is: 0004

Register 0306 is: 000a

Register 0310 is: 0000

Register 0430 is: 0770

Register 0450 is: 2600

Register 0451 is: 0001

Register 0452 is: 0100

Register 0453 is: 0006

Register 0456 is: 0000

Register 0457 is: 6483

Register 0458 is: 0001

Register 045D is: 318c

Register 045F is: 0003

Register 0485 is: 1078

Register 0486 is: 0a05

Register 0489 is: 0001

Register 0496 is: 044c

Register 0497 is: 01c0

Register 04A0 is: 1000

Register 0553 is: 0000

Register 0560 is: 07e4

Register 0561 is: 0400

Register 0562 is: 00fb

Register 0600 is: 0038

Register 0601 is: 0000

Register 0602 is: 0000

Register 0603 is: 0000

Register 0608 is: 007b

Register 0609 is: 0000

Register 060A is: 0b60

Register 060B is: 0005

Register 060C is: 0024

Register 060D is: 0000

Register 0618 is: 0000

Register 0619 is: 0574

Register 061A is: 05dc

Register 061B is: 007d

Register 061C is: 0000

Register 061D is: 0000

Register 061E is: 0000

Register 0620 is: 0000

Register 0622 is: 0000

Register 0623 is: 0000

Register 0624 is: 5511

Register 0625 is: 0000

Register 0626 is: 0000

Register 0627 is: 0000

Register 0628 is: 0000

Register 0629 is: 0000

Register 062A is: 0000

Register 0639 is: 0000

Register 063A is: 0000

Register 063B is: 0000

Register 063C is: 0000

Register 063D is: 0000

Register 063E is: 0000

Register 0648 is: 0120

Register 0649 is: 0000

Register 064A is: 0010

Register 0871 is: 0000

Register 1000 is: 0000

Register 1001 is: 0000

Register 1007 is: 003d

Register 100B is: 0800

Register 1012 is: 0001

Register 1834 is: 8000

Register 1836 is: 0000

Register 3000 is: 0000

Register 3001 is: 0000

Regards,

Anagha

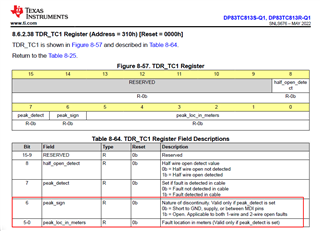

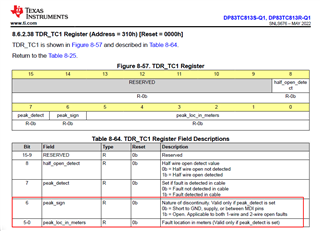

At present, it has been found that there is a half open circuit state in the case of an open circuit, and peak_loc_in_sters is unstable(0~3m). However, in reality, we have not connected the PHY and the harness length is 0m

Hello Li,

I will test this without using a cable/harness length of 0m, and get back to you tomorrow (7/18).

Best,

Anagha

Hello Li,

Was the TDR procedure run before every 0x0310 reg value attached in your previous message? Or were the register values changing every time they were pulled after running TDR only once?

Additionally, is this being tested using TI's DP83TC813 EVM?

Regards,

Anagha

We always follow this operation to set the register and read the address 0x310 register. The value of the address 0x310 register changes between 0x1C0, 0x1C1, 0x1C3, 0x0C0, 0x0C1, and 0x0C3 each time. However, the value of the address 0x310 register should be either 0x0C0 or 0x0C1 to be correct, as the length of the wiring harness is within 1 meter

We are not using TI's DP83TC813 EVM, but our own circuit board

Hello Li,

I will discuss this internally and get back to you early next week.

Best,

Anagha

Hello Li,

At the moment, open fault detection in one wire is not distinguishable from the full cable open fault. This results in a redundancy in the half open detect feature in the DP83TC813. In order to resolve the issue you are seeing with 0x310 values, please re-run TDR with the following correction: 0x306[4] = 0.

This change should result in the expected register values for 0x310.

Regards,

Anagha