Tool/software:

Hi,

When comparing products manufactured in 2015 to products manufactured in 2024, there was a difference in response to EMC noise.

Is "Die Revision Change" in PCN# 20160317001 related to the above issue? If yes, could you tell me about the relationship between the change in Die and EMC noise?

The differences in product behavior between 2015 and 2024 are:

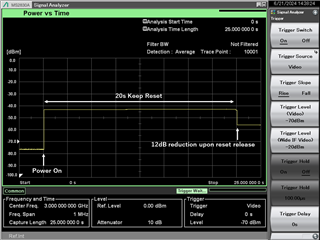

・2015: SATA clock occurs during reset, and the amplitude level of clock-derived EMC noise decreases upon reset release.

The waveform is the result of EMC noise measured by the signal analyzer. EMC noise at 3GHz occurs at the same time as Power On, and after 20s, the level drops by 12dB upon reset.

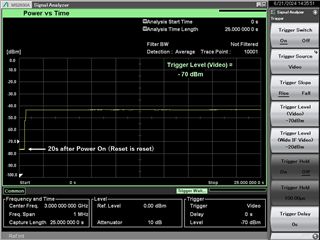

・2024: SATA clock does not occur during reset, clock occurs upon reset release, and the amplitude level of EMC noise does not decrease.

Regarding the waveform, EMC noise of 3GHz is not generated when power is turned on, and 3GHz noise is generated and maintained at the same time when reset is released after 20s.

Best Regards,

Nishie