Part Number: TCA9517

Other Parts Discussed in Thread: TCA9617B

FAQ: Logic and Voltage Translation > IxC >> What is a buffered LOW?

A "buffered LOW" is the output voltage of the buffer when a low voltage input (VIL) is present on the input.

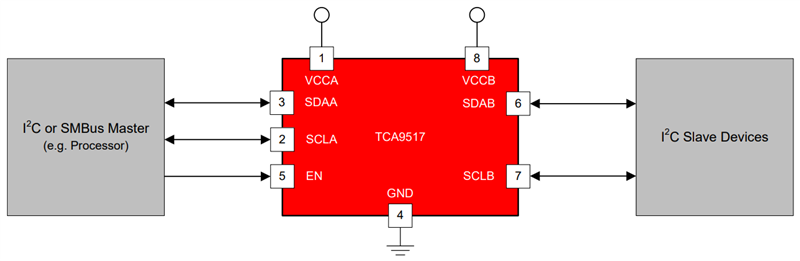

This buffered LOW is commonly referred to the B-side output voltage when A-side is driven, because it is the B-side that contains the static voltage offset (SVO) present on several I2C buffers - TCA9517 / TCA9517A / TCA9617B.

Given that I2C buffers are bi-directional, inputs and outputs can change reference. *note the direction of the arrows for each pin on the buffer.

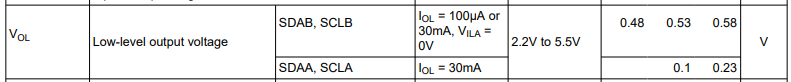

A snippet of the electrical characteristics from the TCA9617B datasheet shows that an input of VILA = 0V will result in an output voltage on B-side VOLB = 0.53 V (typ.) This offset voltage is known as the buffered LOW.

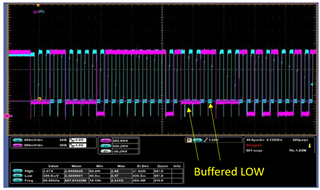

Here is a oscilloscope example of the buffered LOW voltage when driving the A-side of a buffer with a SVO on B-side.