Tool/software:

Dear TI

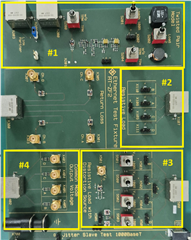

We changed the PCB design and conducted a new test.

(There are two-PHY ICs on the PBA, LAN#0 & LAN#1)

Some failed.

Please guide me on the solution.

[Based on LAN Compliance]

(1) Problem#1(10Base-T) : w/ TPM level is 700mV. (w/o TPM level is 1.4V)

-.Measure 2 items(Link Test Pulse)

-->No TPM(14.3.1.2.1) item is PASS (LAN#0, LAN#1)

-->With TPM(14.3.1.2.1) item is FAIL (LAN#0, LAN#1)

--> I2C register :

mii write 0x0d 0x001F 0x8000

=> mii write 0x0f 0x001F 0x8000

=> mii write 0x0d 0x0000 0x0100

=> mii write 0x0f 0x0000 0x0100

=> mii write 0x0d 0x0010 0x5008

=> mii write 0x0f 0x0010 0x5008

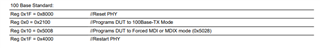

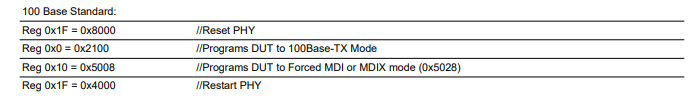

(2) Problem#2(100Base-T) : I tested it with Mode 5 and it failed. Any other setting?

-.Measure 1 items(Return Loss)

-->Transmitter Returen Loss(9.1.5) item is PASS(LAN#0, LAN#1)

-->Receiver Return Loss(9.2.2) item is FAIL(LAN#0, LAN#1)

--> I2C register : (Test Mode 5)

mii write 0x0d 0x001F 0x8000

=> mii write 0x0f 0x001F 0x8000

=> mii write 0x0d 0x0000 0x2100

=> mii write 0x0f 0x0000 0x2100

=> mii write 0x0d 0x0010 0x5008

=> mii write 0x0f 0x0010 0x5008

=> mii write 0x0d 0x0009 0xBB00

=> mii write 0x0f 0x0009 0xBB00

=> mii write 0x0d 0x00D 0x001F

=> mii write 0x0f 0x00D 0x001F

=> mii write 0x0d 0x00E 0x0025

=> mii write 0x0f 0x00E 0x0025

=> mii write 0x0d 0x00D 0x401F

=> mii write 0x0f 0x00D 0x401F

=> mii write 0x0d 0x00E 0x0480

=> mii write 0x0f 0x00E 0x0480

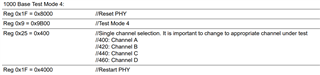

(3) Problem#3(1000Base-T) : shortage of Margin

--> Differential Output Templates With Disturber's Point H is FAIL(LAN#1)

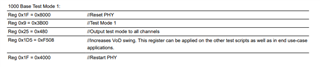

--> I2C register : (Test Mode 1)

mii write 0x0d 0x001F 0x8000

=> mii write 0x0f 0x001F 0x8000

=> mii write 0x0d 0x0000 0x0140

=> mii write 0x0f 0x0000 0x0140

=> mii write 0x0d 0x0010 0x5008

=> mii write 0x0f 0x0010 0x5008

=> mii write 0x0d 0x0009 0x3B00

=> mii write 0x0f 0x0009 0x3B00

=> mii write 0x0d 0x00D 0x001F

=> mii write 0x0f 0x00D 0x001F

=> mii write 0x0d 0x00E 0x0025

=> mii write 0x0f 0x00E 0x0025

=> mii write 0x0d 0x00D 0x401F

=> mii write 0x0f 0x00D 0x401F

=> mii write 0x0d 0x00E 0x0480

=> mii write 0x0f 0x00E 0x0480

=> mii write 0x0d 0x00D 0x001F

=> mii write 0x0f 0x00D 0x001F

=> mii write 0x0d 0x00E 0x01D5

=> mii write 0x0f 0x00E 0x01D5

=> mii write 0x0d 0x00D 0x401F

=> mii write 0x0f 0x00D 0x401F

=> mii write 0x0d 0x00E 0xF508

=> mii write 0x0f 0x00E 0xF508