Part Number: DP83869HM

Other Parts Discussed in Thread: DP83869, DP83869EVM

Tool/software:

Hi

I am designing a product that need a 1000BASE-SX interface.

The computer board I must use has a 10/100/1000/2500MBit copper ethernet interface.

Because of this I intend to use the DP83869HM in the 1000M Media Converter application mode.

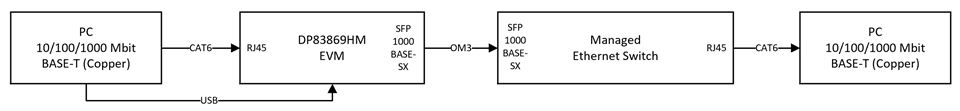

My intended setup is as follows:

10/100/1000/2500MBit copper -> DP83869HM in 1000M Media Converter mode -> 1000BASE-SX SFP -> External Link Partner (during testing I will simulate the LP with an ethernet switch (managed type) with an SFP port).

My goal is to run the DP83869HM in unmanaged mode. I am not planning to use an MCU controller for this product.

I want to force the MAC on the computer side to run at fixed 1000Mbps. The fiber SFP transceiver will run at 1000Mbps.

Can you confirm that the following approach is valid? If anything is missing or wrong, please let me know.

Straps

PHY ADDR set to 0 (single PHY on the bus) -> PHY_AD[3]:PHY_AD[0] all set to 0

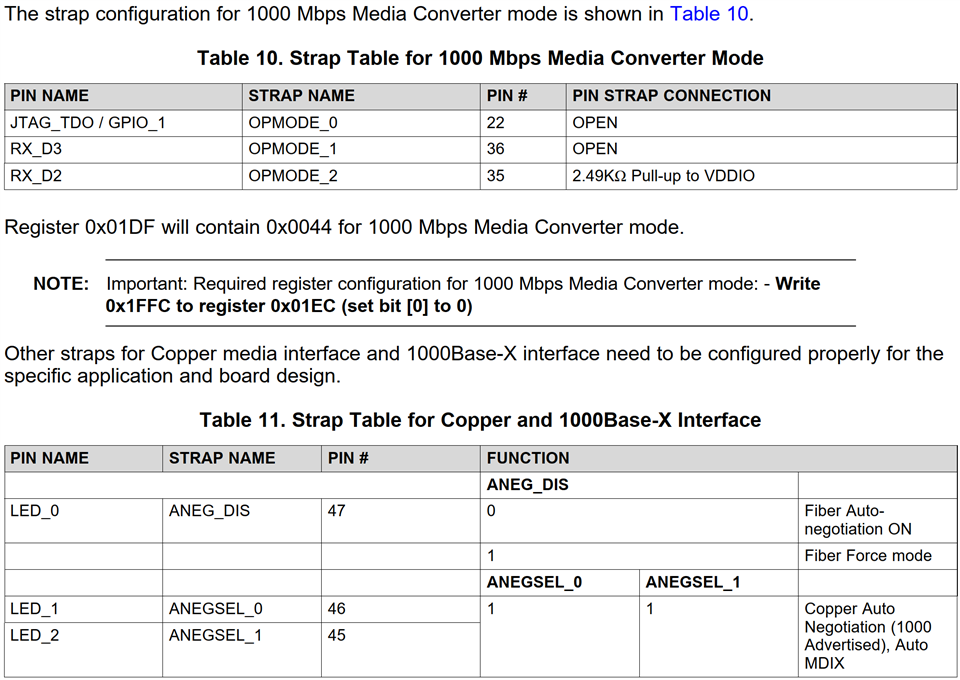

Operation mode:1000M Media Converter -> OPMODE_2 = 1, OPMODE_1 = 0 and OPMODE_0 = 0 -> On EVM: OPMODE_2 = PU (J19 shorted), OPMODE_1 = PD (J10 open) and OPMODE_0 = PD (J11 open).

ANEG_DIS set to 1 to disable auto-negotiation on fiber side and force 1000Mbps -> On EVM: J2 = PU (J2 jumper placed between pins 2 and 3)

ANEGSEL_1 and ANEGSEL_0 both set to 1 to force 1000Mbps between DP83869HM and PC Ethernet MAC (during auto-negotiation) -> On EVM: J4 = PU (J4 jumper placed between pins 2 and 3) and J7 = PU (J4 jumper placed between pins 2 and 3).

MIRROR_EN disabled -> On EVM: MIRROR_EN = PD (J8 open)

LINK_LOSS pass through enabled -> On EVM: LINK_LOSS = PD (J6 open)

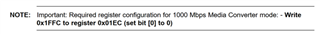

However, in app note SNLA318 the following is mentioned on page 8:

NOTE: Important: Required register configuration for 1000 Mbps Media Converter mode: - Write

0x1FFC to register 0x01EC (set bit [0] to 0)

In my opinion, requiring a register write goes against the unmanaged mode.

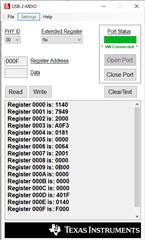

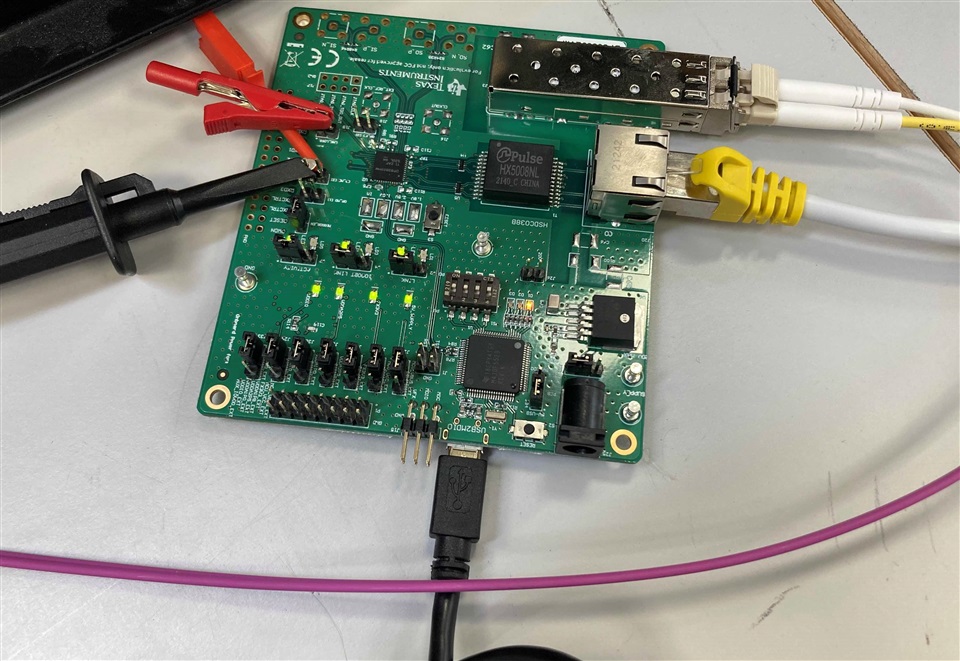

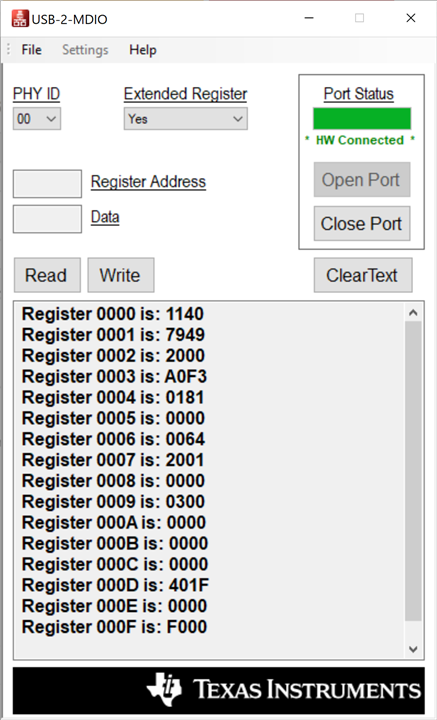

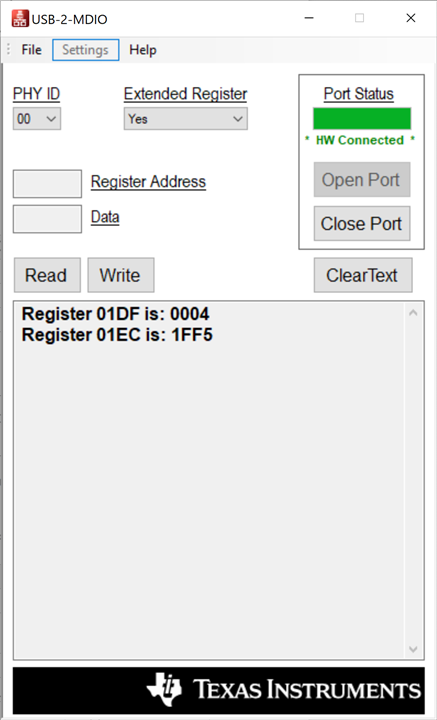

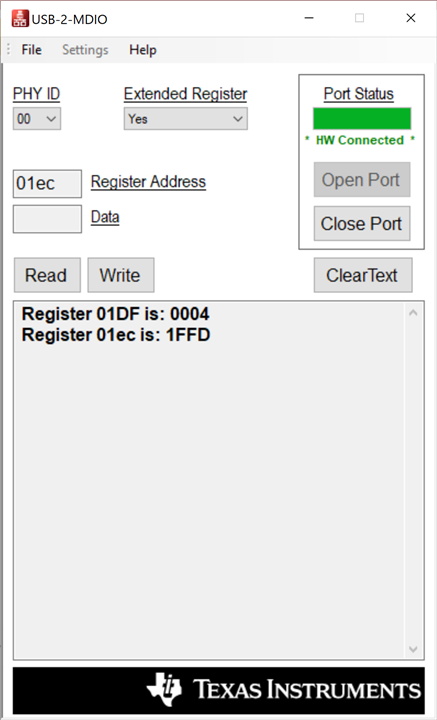

I have tried to test the straps mentioned above on the EVM and I read the following using the USB-to-MDIO tool:

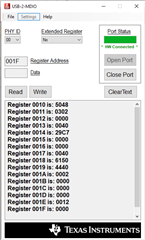

If I short J6 on the EVM I read the following:

This does change the value of the register, but not bit 0. Instead, it writes bit 3 to 0.

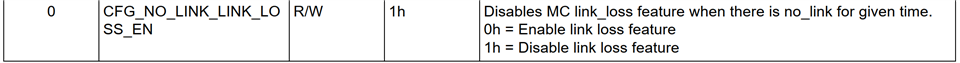

How should I proceed? Is the LINK_LOSS strap tied to bit 0 in register 0x01EC (CFG_NO_LINK_LINK_LOSS_EN)?

The datasheet specifies the default value for the LINK_LOSS strap to be 0, i.e. enabled, so I would think that the pin RX_CLK should be pulled down (via the internal pull down) as default.

Which registers should I read on the EVM?

Reading register 0x0C00 gives 0x0140, which I decode as Fiber auto negotiation disable and forced speed 1000Mbit.

Any other registers I should read?

In addition, app note SNLA305 also specifies that register writes can be needed for 1000Base-X applications.

Please advise.

Regards

Lars