Other Parts Discussed in Thread: DP83869HM

Tool/software:

Hello,

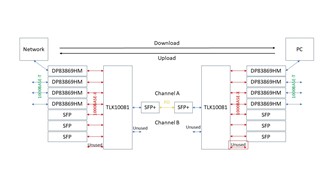

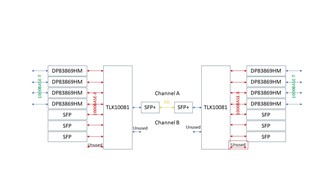

I'm currently using a TLK10081 with 7 lanes (4 Ethernet lanes and 3 SFP lanes) as it follow :

My problem is that I have asymmetrical performances by passing through the TLK10081 when performing a speedtest

With the TLK10081 :

Speedtest results :Download ~ 800Mbps Upload ~ 50Mbps with packet loss

Direct connection as reference, without TLK10081

Speedtest results : Download ~ 800Mbps Upload ~ 800Mbps without packet loss (direct transmission between two DP83869HM is ok with symmetrical performances).

TLK10081 config I use :

read 0x02

read 0x06

write 0x00 0x8610

wait 1sec

write 0x01 0x0302

write 0x02 0x831B

write 0x06 0x8114

write 0x8009 0xFC02

write 0x8019 0xFC02

write 0x1C 0x002C

write 0x1D 0x002C

write 0x17 0x0ABC

read 0x02

read 0x06

wait 5sec

write 0x17 0x02BC

Do you have any recommandation or anything that I can change in the config to solve this issue ?

Thank you in advance.