- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi,

1. Does the SN65DP159RSBR have a function to monitor the status (DC level, etc.) of the HDMI output signal (HDMI_CLK or HDMI_Dx) other than the status of the HPD_SNK input and stop the HDMI output signal?

2. This is a similar question to 1, but what exactly does the signal detector circuit result in "When HPD asserts, the device CDR and output will enable based on the signal detector circuit result" in chapter 11.1 Power Management of the datasheet do?

Best regards,

Hiroshi

Sorry, our customer have an additional question.

3. During input power momentary power interruption testing, we are experiencing a problem where the re-timer does not start properly.

When the power is interrupted momentarily, the following occurs.

- VDD1-4 (1.1V system) drop to almost 0V → then return to 1.1V.

- VCC1,2,I2C_EN (3.3V system) voltage remains at 1V → then return to 3.3V.

- OE is left OPEN and connected to 0.1uF.

After reaching the above state, it cannot return to normal (why?

It can return to normal when 3.3V drops to 0V, so I think it's because the internal circuitry has not completely self-reset when 1V remains, is this understanding correct?

Best regards,

Hiroshi

1. Does the SN65DP159RSBR have a function to monitor the status (DC level, etc.) of the HDMI output signal (HDMI_CLK or HDMI_Dx) other than the status of the HPD_SNK input and stop the HDMI output signal?

No this device does not have a function to monitor the TX out

2. This is a similar question to 1, but what exactly does the signal detector circuit result in "When HPD asserts, the device CDR and output will enable based on the signal detector circuit result" in chapter 11.1 Power Management of the datasheet do?

This is an internal signal detection circuit which is based of the PLL status in the retimer

3. During input power momentary power interruption testing, we are experiencing a problem where the re-timer does not start properly.

When the power is interrupted momentarily, the following occurs.

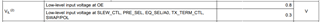

In this power stage we see that the the VCC is never fully set to 0V it is held at 1V. This means that the voltage level seen at OE is higher than the VIL threshold and thus the device is never fully reset as the OE is tied to VCC. This places the device into an unknown state.