- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

Tool/software:

A customer is facing some issues during development using DP83825I and has some questions.

Q1) During the EMC certification, the PHY LINK is continuously disconnected during the Conducted Susceptibility network 10V test. Are there any solutions or countermeasures?

Q2) During 100Mbps operation, the network environment sometimes drops to 10Mbps. Is this a specification that changes automatically? Are there any registers that need to be set for such behaviour?

Q3) If I want to fix the speed of PHY to 10Mbps, could you please confirm the registers that need to be set and their values?

Q4) Is it correct that I can refer to the value of bit 14 of register 0x10 to check whether MDI or MDIX is operating?

Q5) It seems to be related to the question of Q4, Bit 14 of Register 0x19 is set to force MDI/X. If I change the corresponding pin setting, will the value of Bit 14 of Register 0x10 also change?

Q6) Could you please explain what the Robust_Auto_MDIX feature is?

Q7) Please review the attached circuit below. (Please check if there are any incorrect or parts that need to be modified.)

Schematics (DP83825I, PHY).pdf

Please check. Thank you.

Hi Grady,

Q1)

Please refer to section "4.7 IEC 61000 4-6 CI" in below appnote for debug procedure:

https://www.ti.com/lit/an/snla466a/snla466a.pdf

Q2)

If link fails during 100Mbps operation, auto-negotiation will downgrade to the next lowest speed for link.

To validate link quality in 100M, I recommend testing with 10M auto-negotiation advertisement disabled (register 0x4[6:5] = '00'). I expect link will not downgrade in this case, but please confirm if packet errors are seen.

Q3)

If the link partner has auto-negotiation enabled, write 0x4[8:7] = '00' to disable 100M advertisements and force 10M.

If link partner has auto-negotiation disabled, write 0x0[13:12] = '00' to force 10M speed.

Q4)

That is correct, 0x10[14] reports MDI/MDIX status.

Q5)

I expect this status bit to change for forced MDIX.

Q6)

Please refer to this thread:

Q7)

Please fill out and return this schematic checklist ("Pin Wise Checklist" sheet):

DP83825_Schematic_Checklist.xlsx

I can help provide additional feedback afterwards.

Thank you,

Evan

Hi, Evan

Thank for response.

There is an additional inquiry from the customer.

First, the Schematic Check List you requested last time is being confirmed with the customer.

Q1) In the case of the DP83825I applied product, network disconnection occurs in a specific band (100~115MHz or 125~135MHz) during the RF Electromagnetic Field Immunity (RI) CE standard test, so I would like to inquire about related countermeasures.

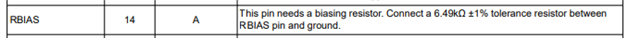

In addition, while checking the TI PHY document, it seems that the RBIAS pin of the DP83825I is related to the RI test, so I would like to inquire about that pin as well.

Q2) What does the RBIAS pin do?

Q3) The DP83825I datasheet says to apply 6.49kΩ to the RBIAS pin, so I applied 6.49kΩ. What happens if I increase or decrease the resistor value?

[Schematic attached]

Please check. Thank you.