Other Parts Discussed in Thread: LMH0344,

Hi, all.

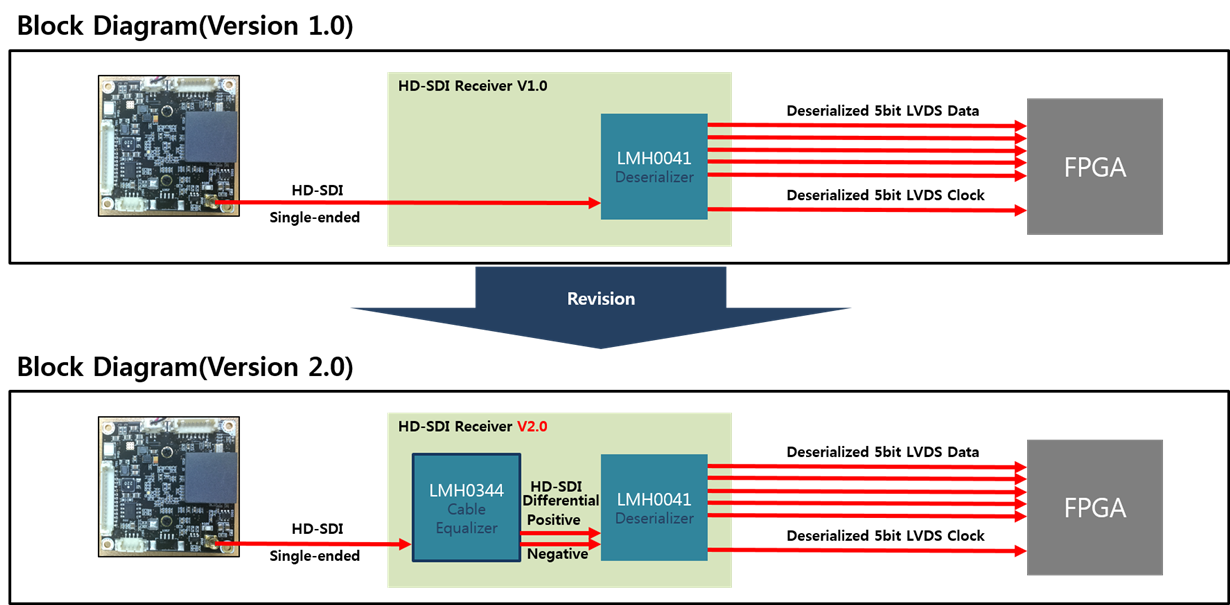

I designed HD-SDI DES(Receiver) Board of 2 versions below as below.

But it does not all work well.

The FPGA(Zed Board) did not recognize the LVDS signal well.

I would like to know what is wrong.

Please see below details.

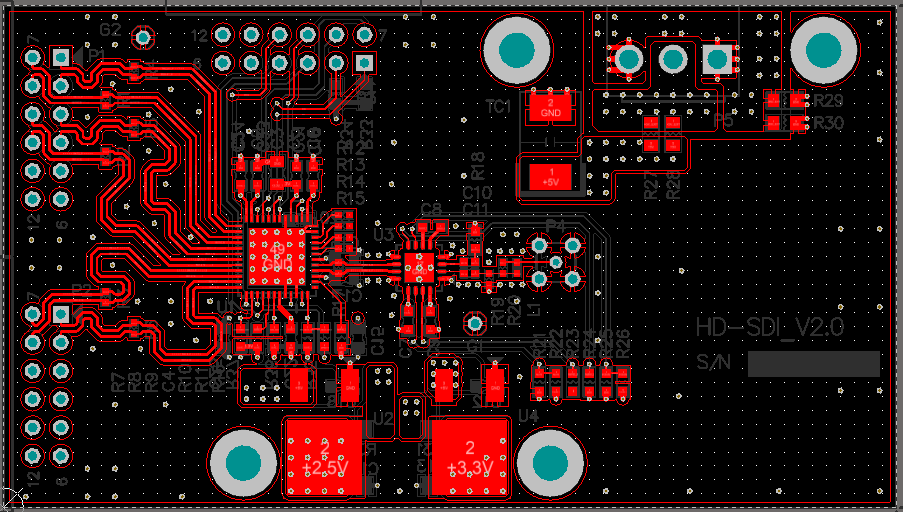

V2.0 PCB Top side

LVDS output trace impedance is 100 ohm (differential) on PCB.

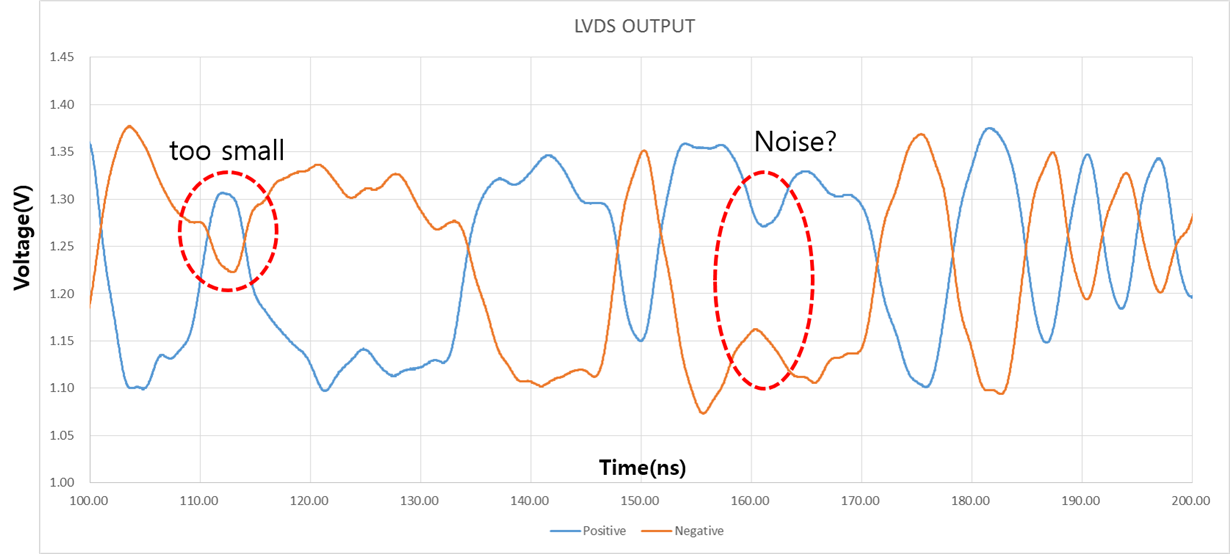

The FPGA did not recognize the LVDS signal. (Zed Board)

LVDS Data output is too strange as Below .

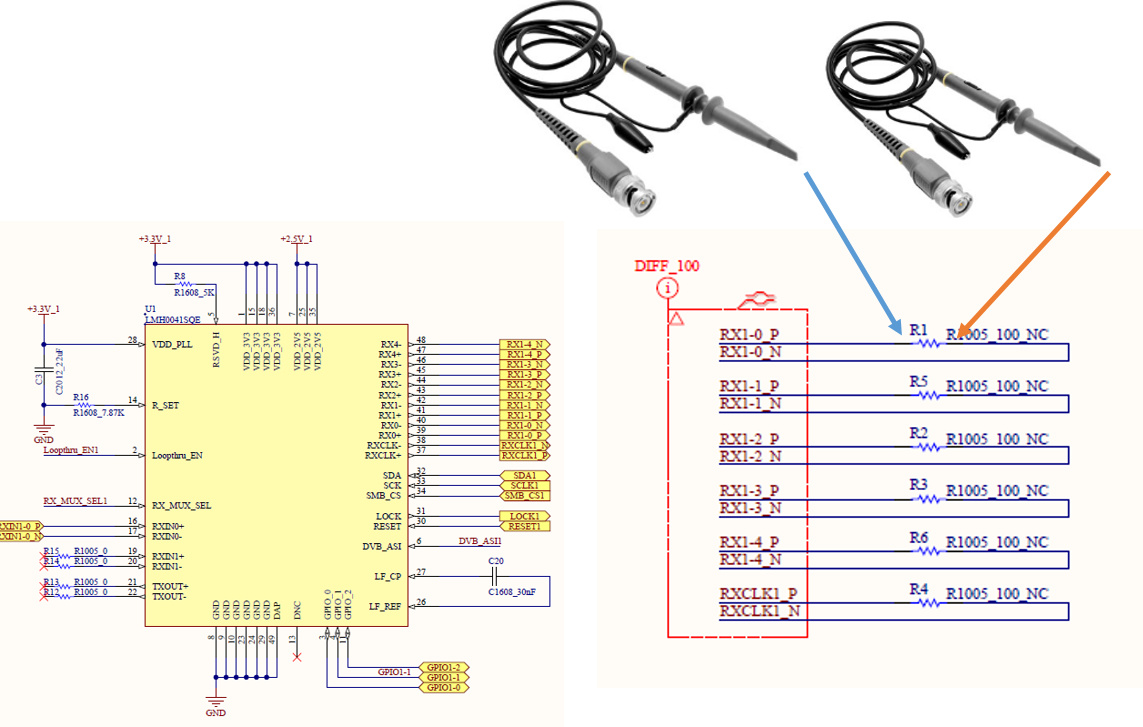

Measurement environment

* C20 uses 27nF instead of 30nF.