Part Number: DP83822I

Other Parts Discussed in Thread: TIDA-00928

Hi

We have a problem with the DP83822IRHBT when exposed to an ESD pulse as low a 6KV contact to chassis.

The problem is that it loses the connection for a couple of seconds when the instrument chassis is hit by a ESD pulse.

(The led on JS3 turns off and we can't ping it from a PC)

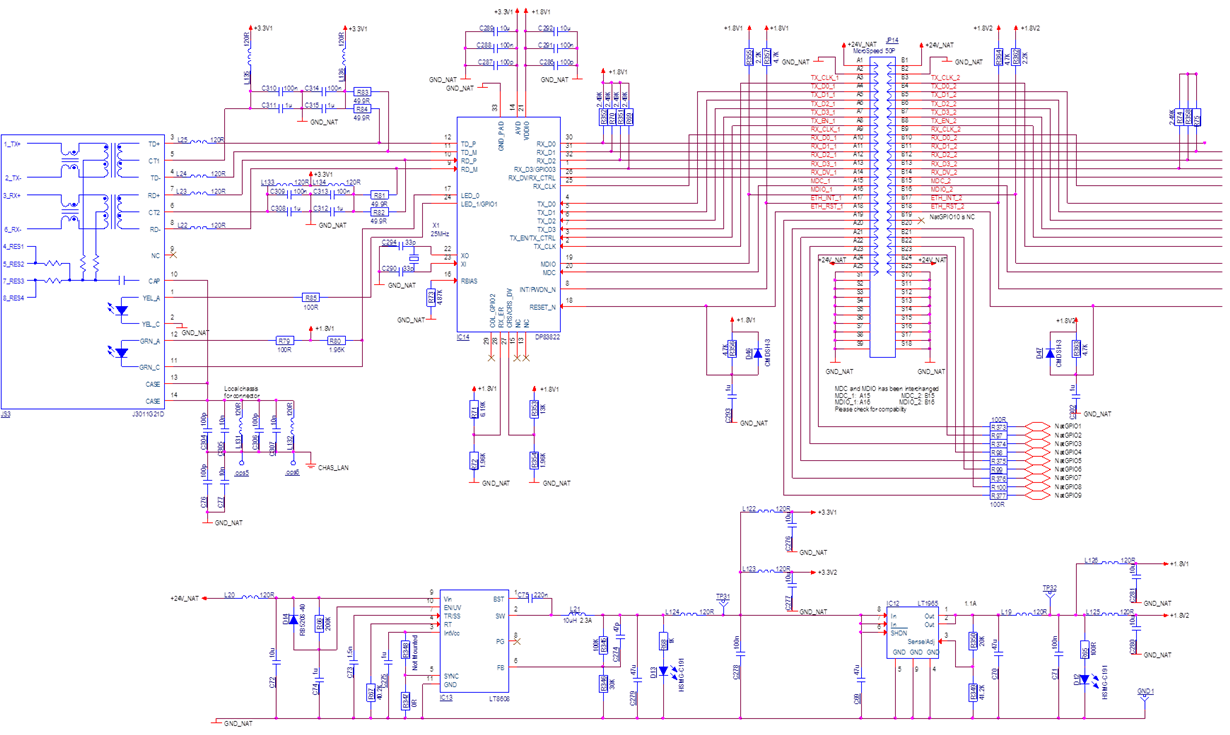

Below you can see the schematics:

Connector JP14 is connected directly to the Ethernet port on a ZYNQ processor.

The ZYNQ processor is not affected by the ESD pulse.

The DP83822 have exactly the same problem even if we remove the ZYNQ from the circuit (The led on JC3 still turns off for a couple of seconds).

On the same PCB we have exactly the same circuit except that DP83822 is exchanged with KSZ8895. Here we have no problems with ESD.

We have tried to place tranzorbers between DP83822 and JS3. It had no effect at all.

The question is: Why do DP83822 loos the connection and what can we do about it?

Could it be that some of the values in the many registers can be programmed to make the DP83822 more robust?

Best Regards

Søren