HI ,

I am using DS90UB914 de-serailizer to interface digital camera which having ds90ub913 in it .

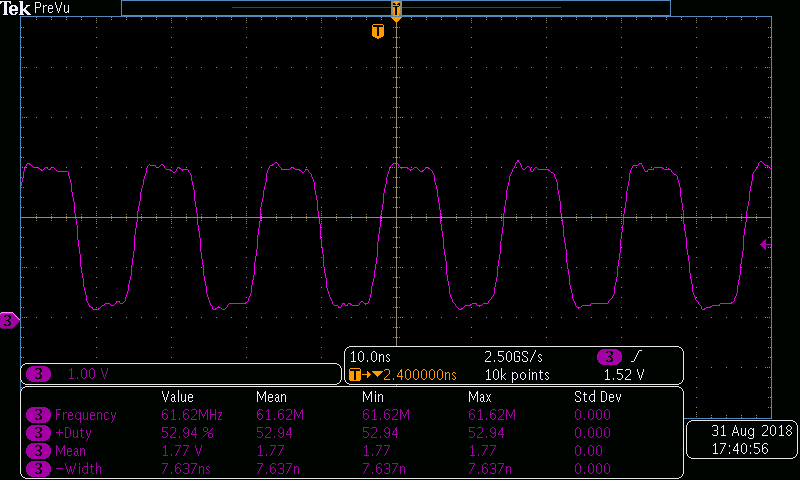

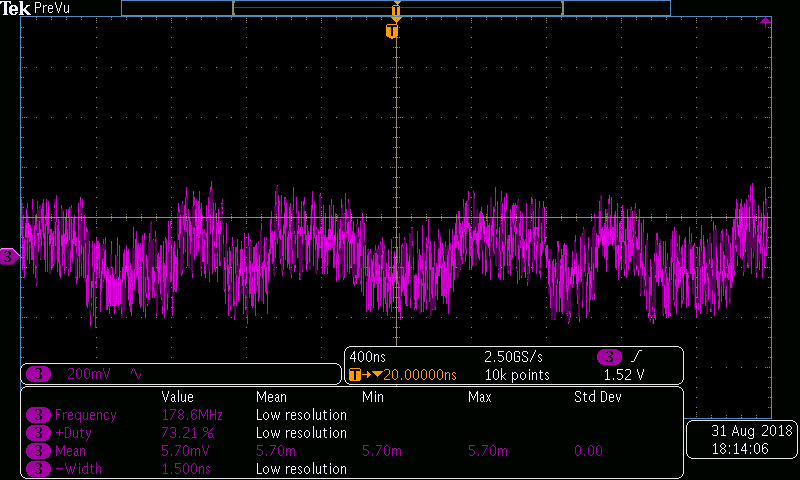

my camera is YUB422 8 bit.but i am using de-serailizer in 10 bit mode .i am getting output from de-serializer but also getting parity error in parity error resister .one more thing in status resister of ds90ub914 lock bit is continue keeps toggling .

any one tell me is this due camera is 8 bit and de-serializer is 10 bit ????