Part Number: TPS65987D

Other Parts Discussed in Thread: TPS65982D,

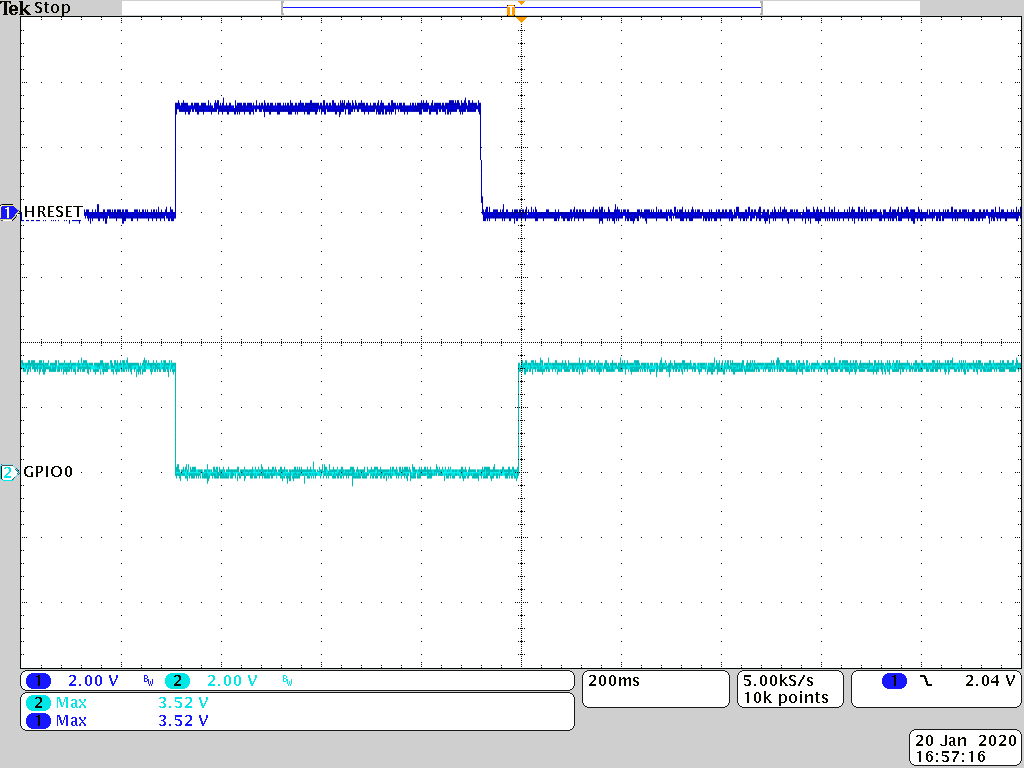

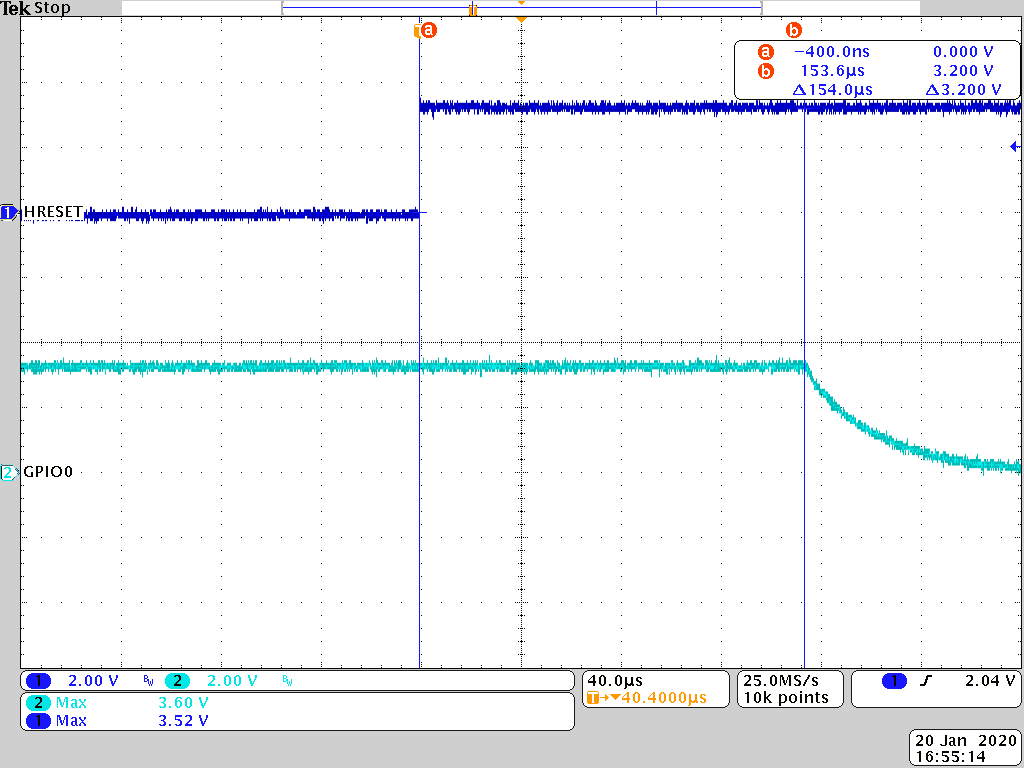

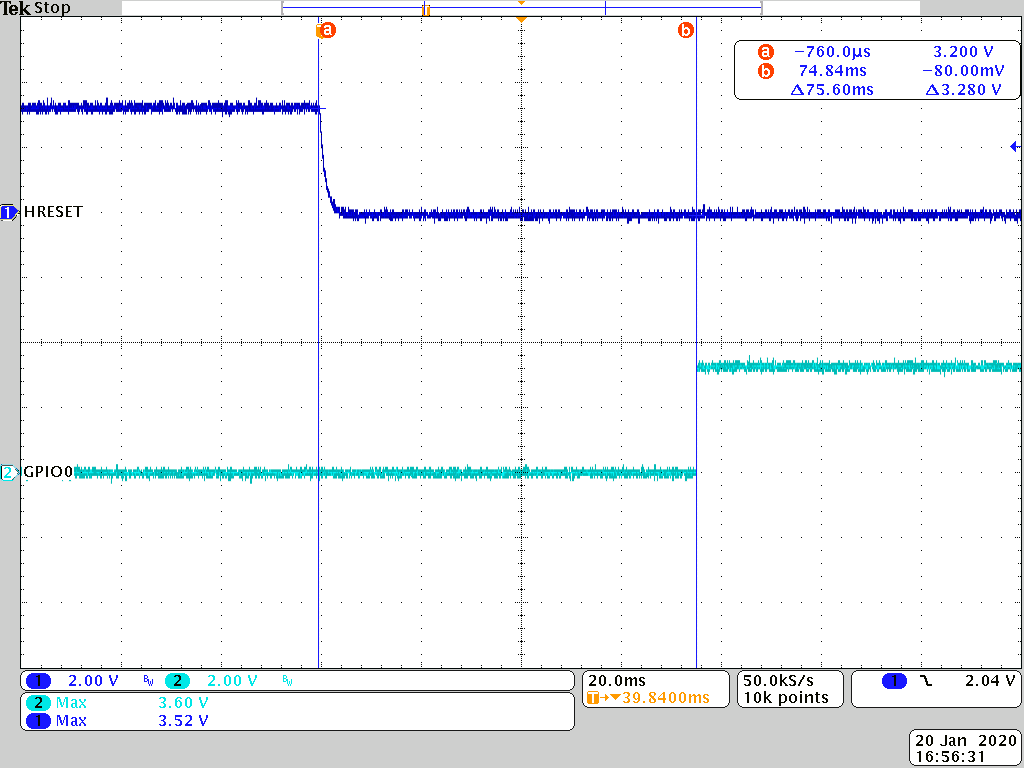

Can you confirm that the HRESET pin information is as shown in datasheet sections 6.1 Absolute Maximum Ratings for I/O Voltage and in sections 6.13 I/O characteristics, are as shown for the GPIO pins.

In the previous part, TPS65982D, the HRESET pin characteristics were shown in a separate table. Is this pin now considered and characterized as a GPIO?

We want to confirm that the TPS65987D HReset can be driven by a 1.8V port and what timing need be applied to it, if different from the GPIO timing.