Other Parts Discussed in Thread: TCA9539

Hi,

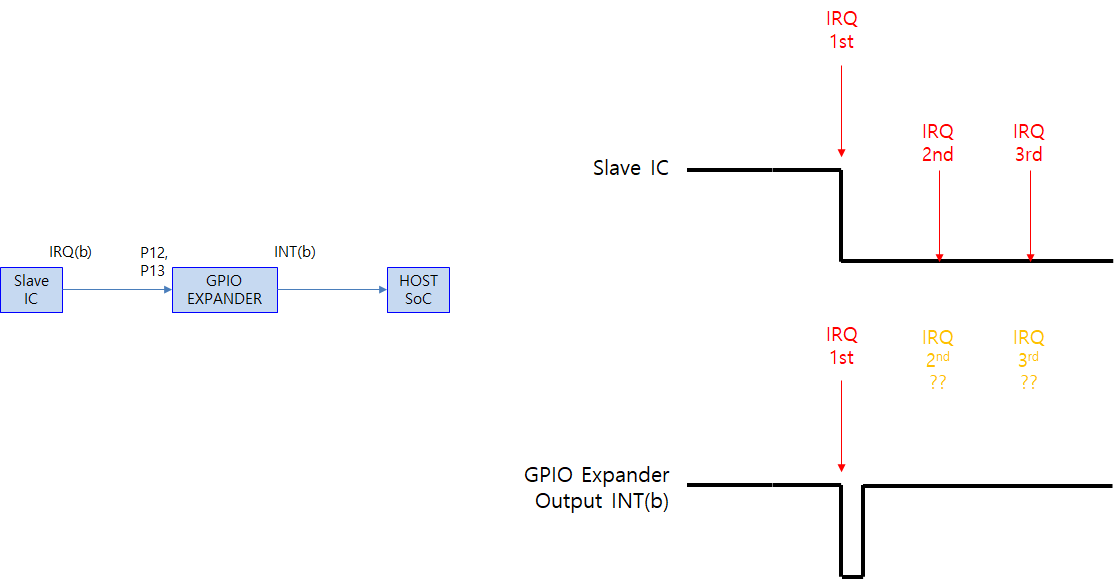

current system is configured like below. (in the middle of GPIO Expander: TCA9539)

but, in HOST SoC, I think, it seems like, SoC doesn't receive every IRQ from Slave IC.

and I have several questions :

q1) GPIO expander can make IRQ output about every rising / falling edge, in default register setting ?

q2) If the IRQ of slave IC (GPIO expander input) keeps going on LOW,

GPIO Expander cannot make IRQ output ?

q3) is there any recommendation for related register ?

Thanks.