Part Number: SN65DSI83

We have a product based on the NXP i.MX8M CPU that also uses the TI DSI83 MIPI DSI Single-Link LVDS Bridge to provide video. We are running the 4.14.78 version of Linux built with the Yocto tools. This code includes a third-party driver (sn65dsi83_brg.c) for the DSI83 coded by CopuLab Ltd.

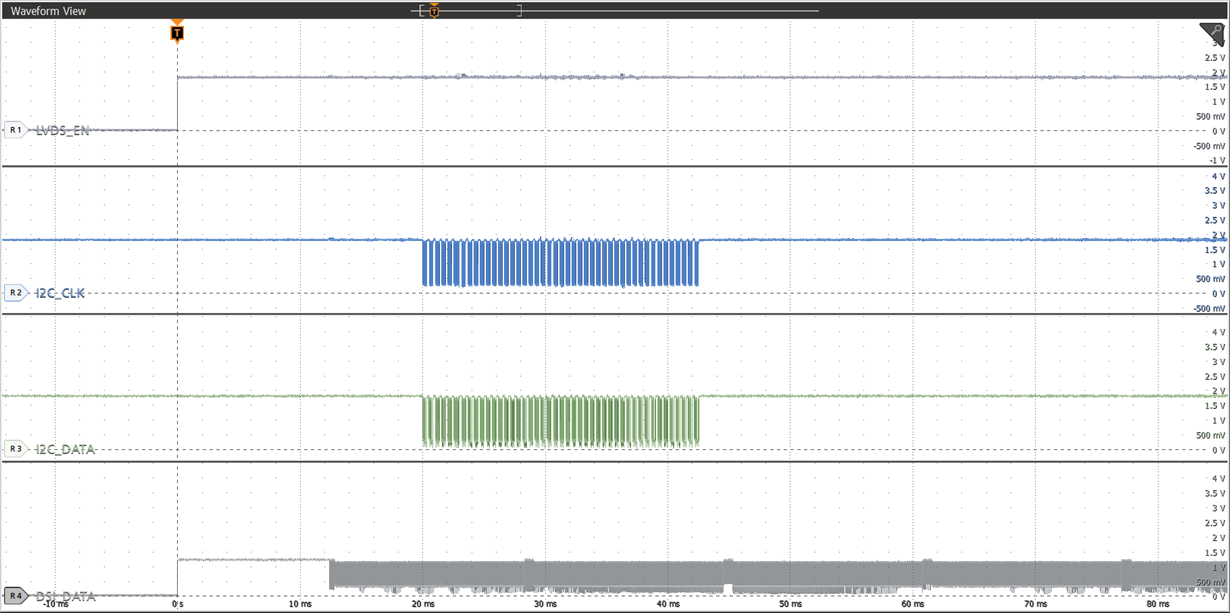

We have an issue where the LVDS display does not always provide video. Most of the time boards work fine but periodically the backlight will come on but nothing is displayed. One thing we noted is that the CHA_UNC_ECC_ERR bit in register 0xE5 is always set when the display does not work. This indicates an uncorrectable ECC error. We believe the root cause of this failure is in the initialization sequence.

Currently we are reviewing the initialization sequence to ensure it follows the Recommended Initialization Setup Sequence found in the device data sheet on page 15.

We are also reviewing the driver source code. One thing we noted is that the driver does not follow Init seq 10 or 11. This clears and verifies that CSR 0xE5 is a zero. In fact, usually we see multiple error bits set and ignored even when the LVDS video display works.

Is there any hardware and/or software support TI can provide to assist with this issue?

Is there any other Linux driver for this device?