Hi Team, we would like to seek assistance, on a temperature of about 65°C or more, measured on the top,

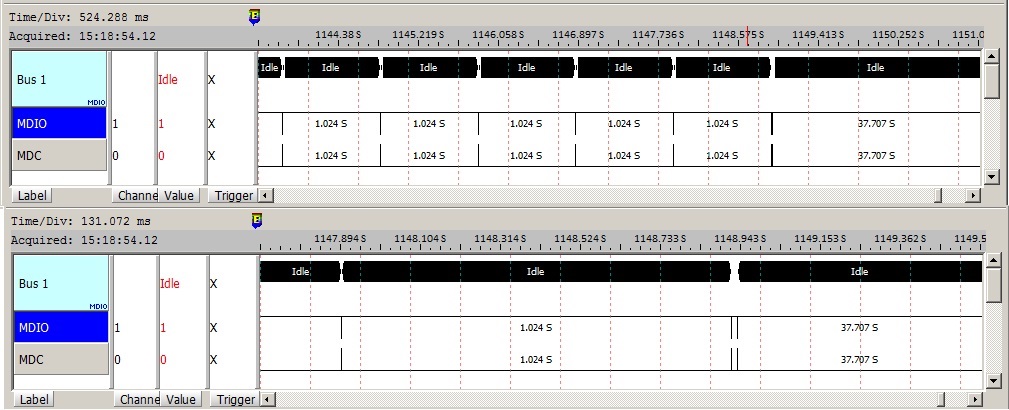

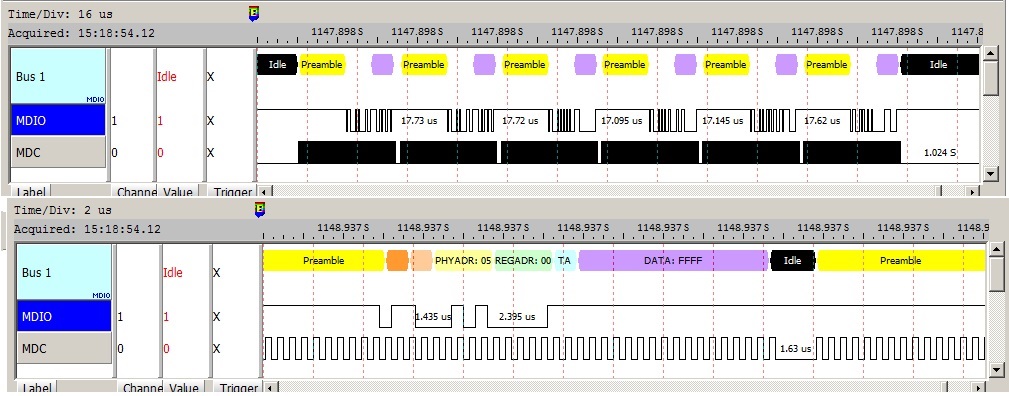

There is a link down of ethernet communications (Gbit) and termination of MII serial messages. Supply voltages and 25MHz clock are ok. The skew programmed (RX and TX) was 1.5 or 2ns.

We would like to know if you are encountering a similar problem?

Thank you in advance.

Regards,

Mark