Part Number: DP83867CR

Hello,

We are having a similar issue on a custom board design as described in this post:

In our design we are using a Zynq Ultrascale+ with four DP83867s connected on a shared MDIO bus.

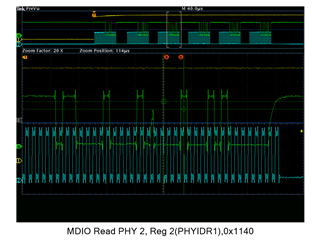

I have checked and verified strapping, MDIO addressing, MDIO timing and the actual MDIO communication to and from the PHYs on the MDIO bus and can provide relevant scope plots. I have also checked power and do not see any apparent issues.

The clock inputs to the four PHYs are driven by a single 25MHz clock that goes into a 1.8V 1:4 clock fanout buffer. Each PHY gets its own clock from the fanout buffer.

In our simplest case, we have 4 phys powered and then we assert BCMR bit 11 in one of the PHYs to transition it into power down state. Subsequent MDIO transactions to the powered down PHY are good, but queries to the other PHYs on the MDIO bus return invalid register data which can be seen on the bus transaction.

I have verified the MDIO bus transactions and the other PHYs are being addressed and correct register address being sent, but are returning sometimes 0xFFFF, 0x00FF, 0x1140 (FYI: this happens to be the default BCMR register value) or sometimes other values. Once the power down state of the single PHY is restored or a RESET all MDIO interfaces begin working normally.

The issue is on the PHY or state of the MDIO interface of the PHY(s) not the host controller nor FW driver.

Is anyone familiar with this issue or state of the MDIO interface and can provide how this issue was resolved?

Thanks,

Mike