Hi teams

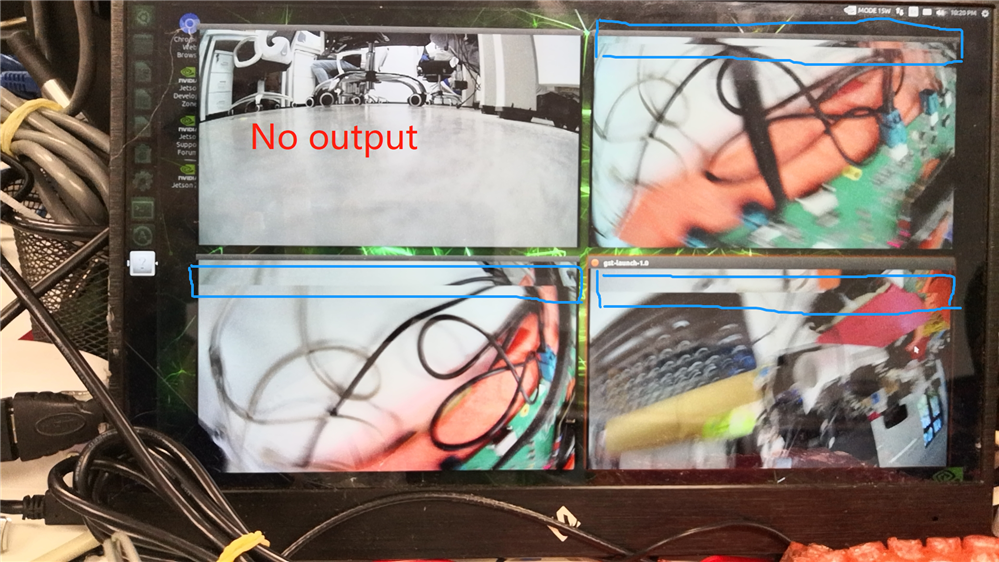

Recently,we are working on 960 deser chip.When I preview the picture,there is some problem.

I use the sensor of 953 ser 1920x1080

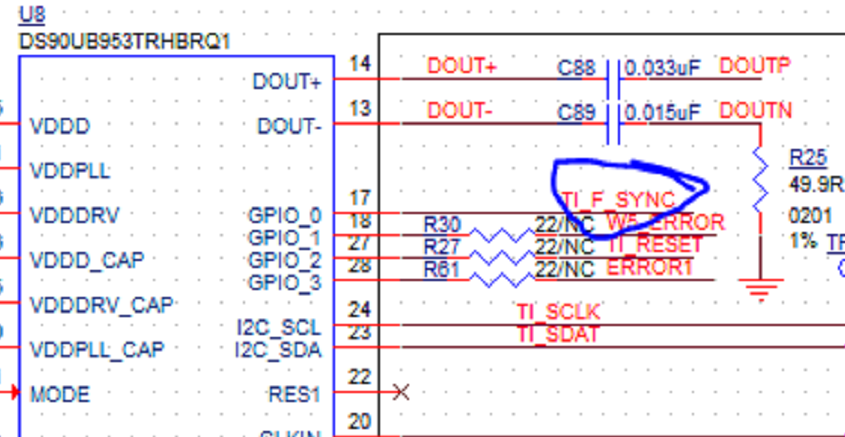

It use Internally generate frame sync.

The reg I set as below:

i2cset -f -y 8 0x3d 0x6F 0xAA

i2cset -f -y 8 0x3d 0x33 0x03

i2cset -f -y 8 0x3d 0x33 0x03

i2cset -f -y 8 0x3d 0x20 0x0C