Hi Sir,

I have attached the schematic design DP83869PHY chip and AFBR-5803 interface section with the following configuration also.

Please find the below PHY configuration details and confirm the configuration is correct or not

- Device PWR supply is 2 supply configuration but considered 1.8V section is "No-load" in the design.

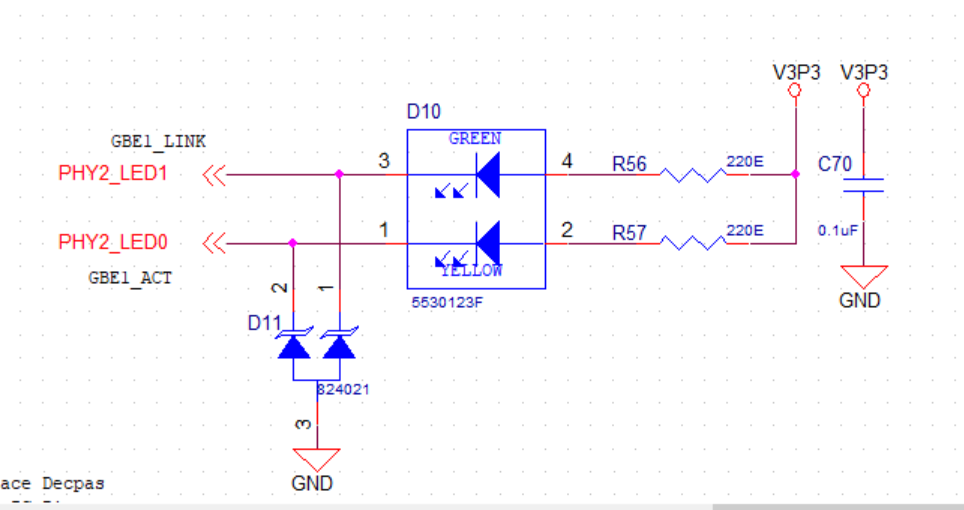

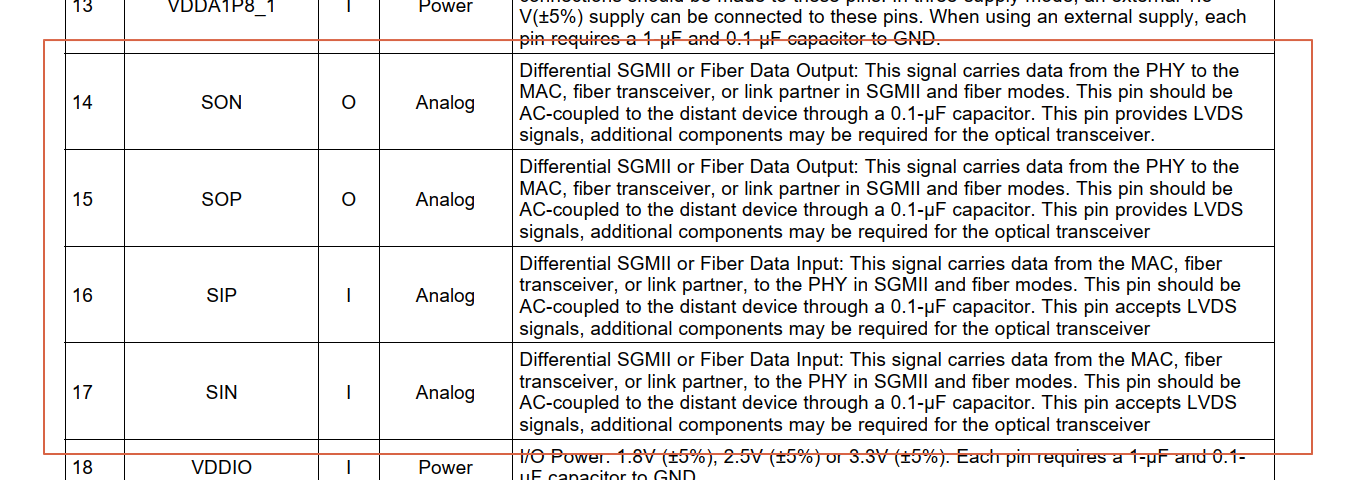

Please confirm the 1.8VDC bus is required for the 100FX fiber interface. The used supply voltage in the design is 3.3VDC, 2.5VDC & 1.1VDC. - Whether AC coupling capacitor is required for FX OUTPUT signal to Fiber transceiver module. Please check the 0.1uF added on the AFBR-5803 is OK or not.

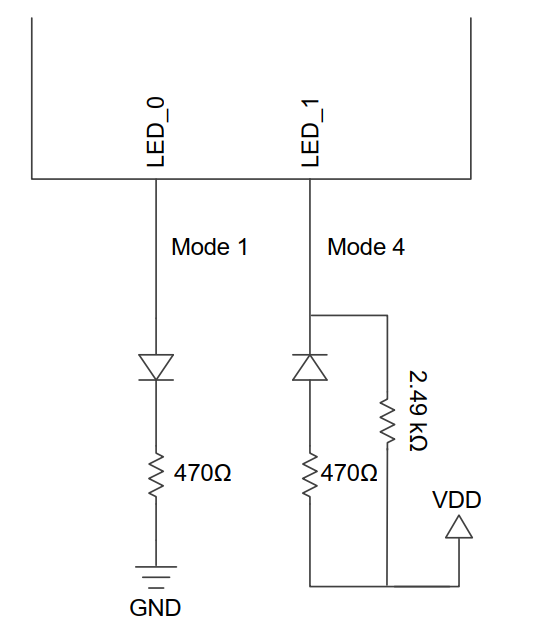

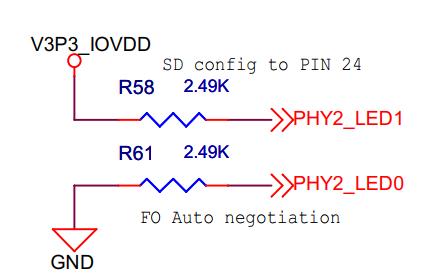

- PIN 24, JTAG_TDI pin configured as "Signal detect " of SC-FO transceiver. Provide pull-up to the LED1(pin-46 of IC) to configure the pin to "SD". Also please check the resistor value used for pull-up the 4.7K pin is OK or not.

- LED0 used for FO auto-negotiation. Please check the configuration also.

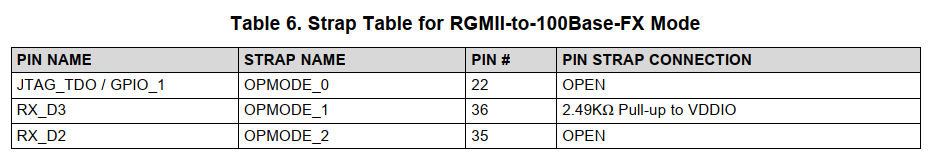

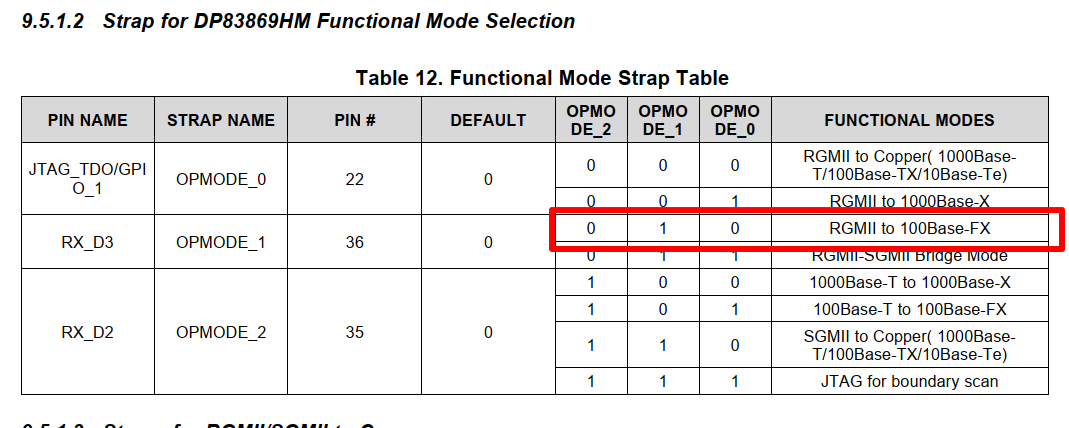

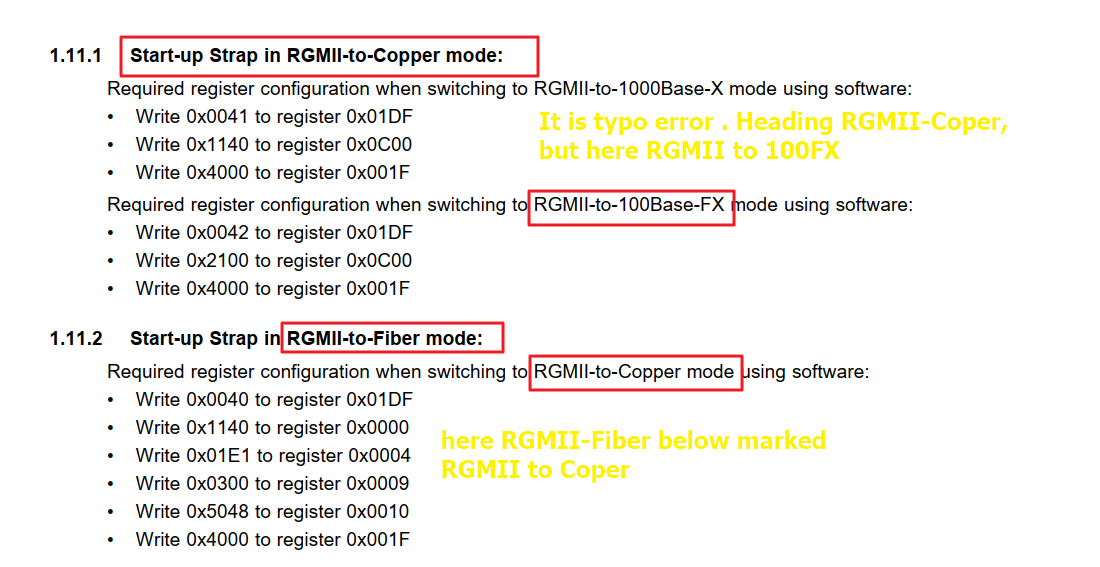

- Please confirm the RGMII to 100FX mode section resistor configuration. Also, crosscheck the resistor values are OK or Not.

- Please confirm the PHY address configuration of "1010" is using resistor strap and resistor values are ok.

- Please confirm the unused JTAG pins need to pull-up or Pull Down

- How to set the LED one for FO to connection detect and the other for FO Activity module. It is set through software or the PIN strap method. Please confirm.

- How to disable the CLKOUT.

Please find the attached schematic.DP83869PHY_100FX SC_FO.pdfDP83869PHY_100FX SC_FO.pdf