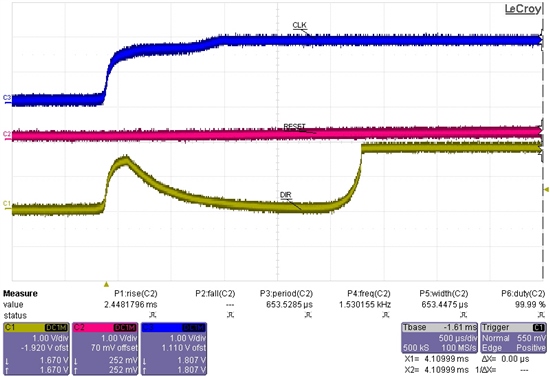

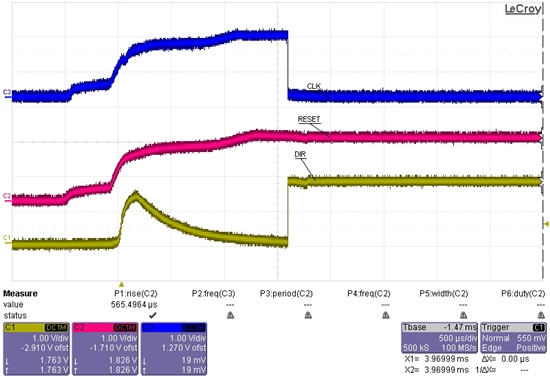

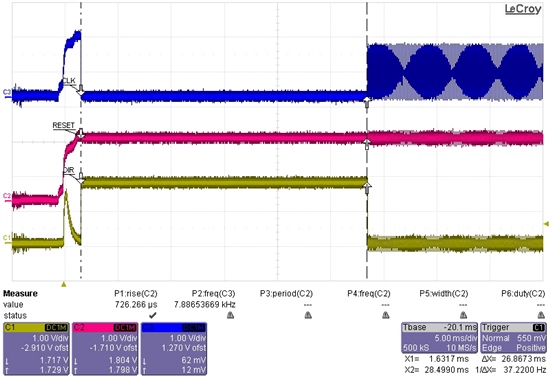

According to figure 6-1 of data manual , ulpi_dir is asserted high after power supplies(before RESETN deasserted)

But ulpi_dir is asserted after RESETN deasserted in my verification environment.

So the strapping value can not be latched correctly, ulpi_clk is not 60MHz.(it is 120MHz ,low power mode)

How to solve the problem?(my crystal input clk is 40 Mhz, refclksel0 =1 ,refclksel0 =1)