Other Parts Discussed in Thread: SN74HCS74

Hi

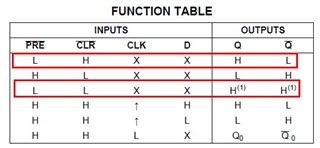

I would like to know what timing does SN74LVC2G74-Q1 sample the high/low level of input ?

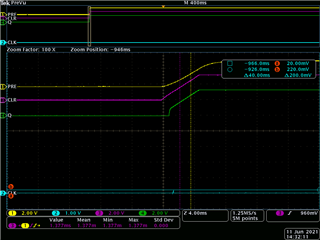

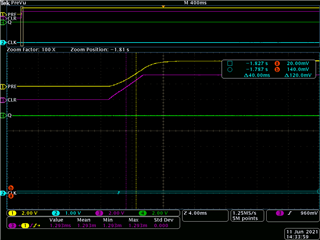

in the case below, Vcc, D, and CLR connected to Vcc. The PRE pin connected to Vcc with a RC delay.

I discovered that the Q is outputting since the Vcc is not ready. Is that a normal performance ?

I found the Q didn't output sometimes when I reboot.

after all, I want to know the following 2 question.

1. What is the sample timing of input ?

2. I want to make Q output high without CLK input when I boot my device, how can I make it stable ?

Thank you!!!