Hi team,

We have a question about D-Type Flip-Flop /CLK issues in ESD test need your support.

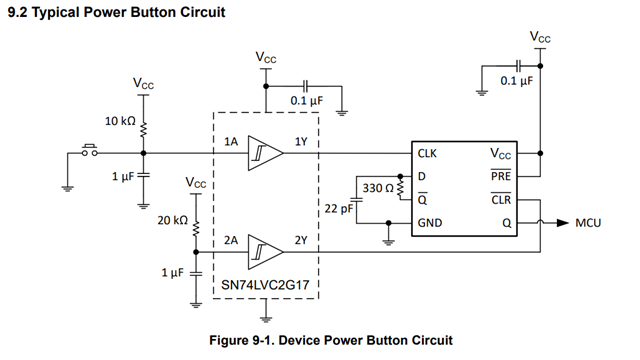

SN74LVC1G74 is used in system, we find that /CLK will be affect and change to low when conduct ESD test, which lead to a wrong signal to output.

Do we have solutions for this problem?

If another suitable device can solve this problem, you can recommend it. Form my knowledge, may be add a delay time for response /CLK can solve this problem, please give your command. Thank you!

BR,

Darren