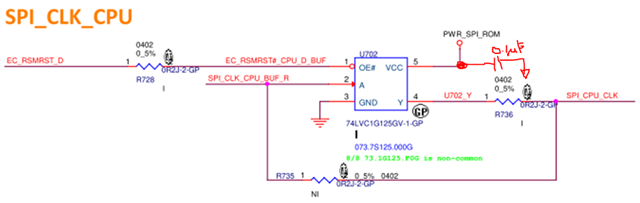

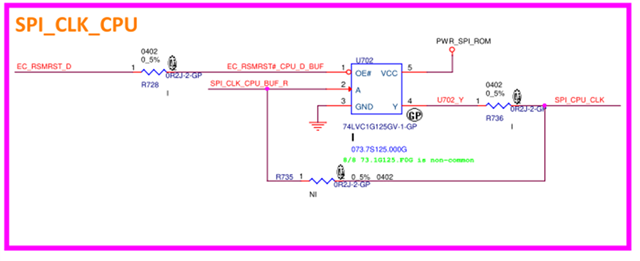

Other Parts Discussed in Thread: SN74AUC1G125,

Hi team,

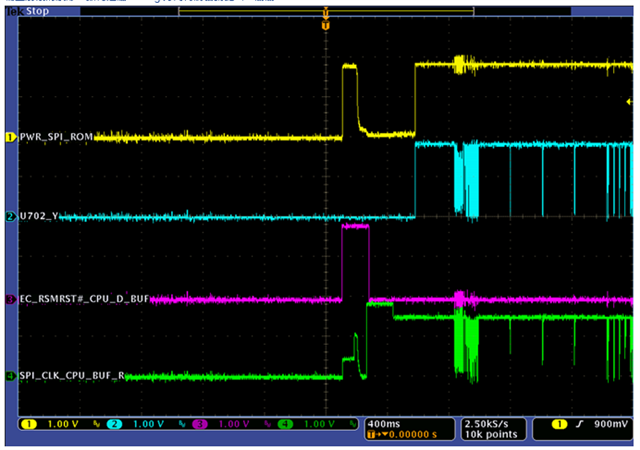

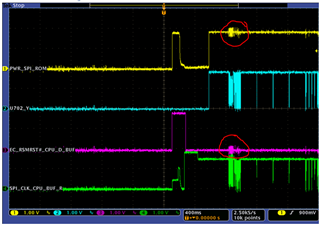

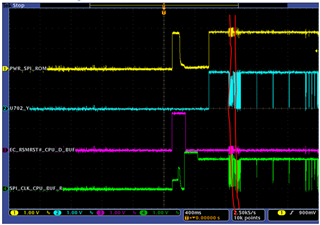

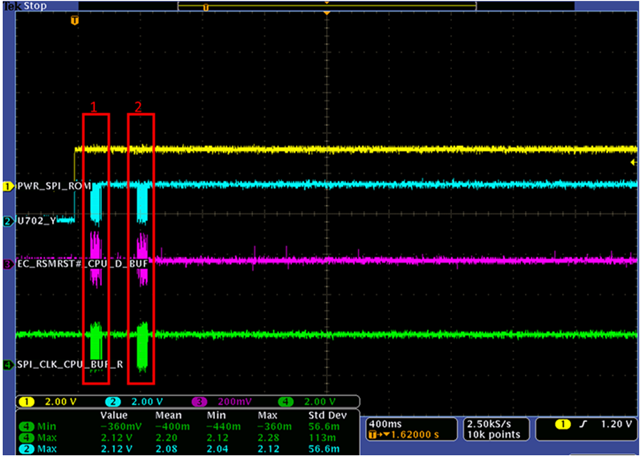

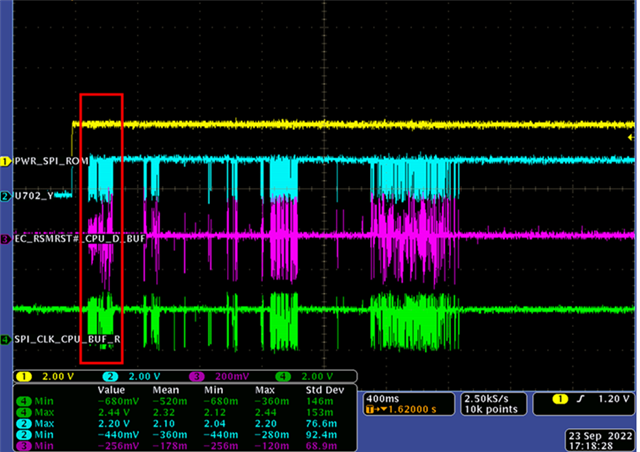

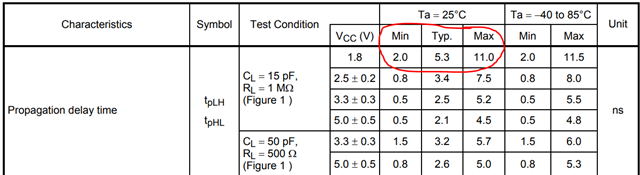

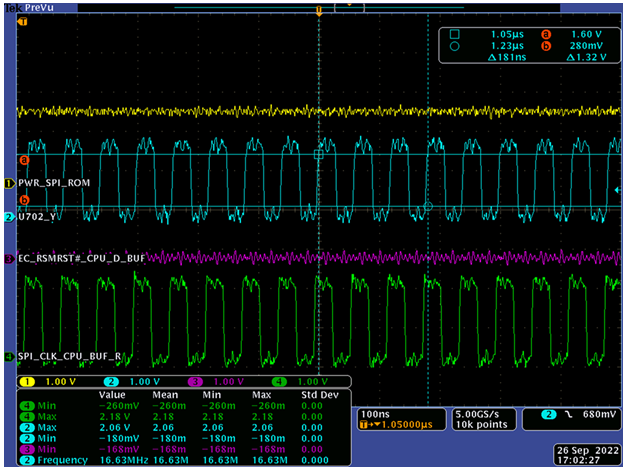

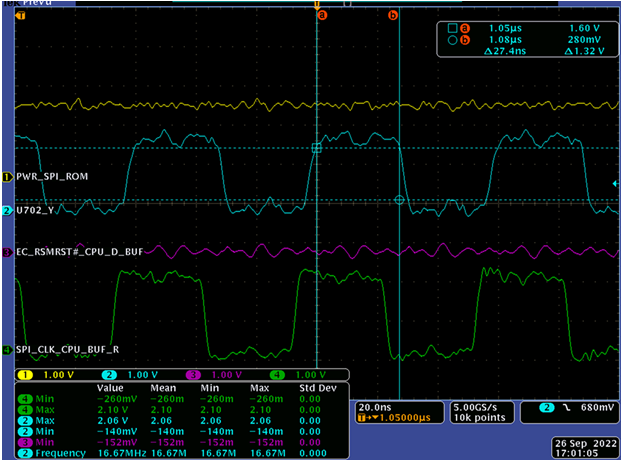

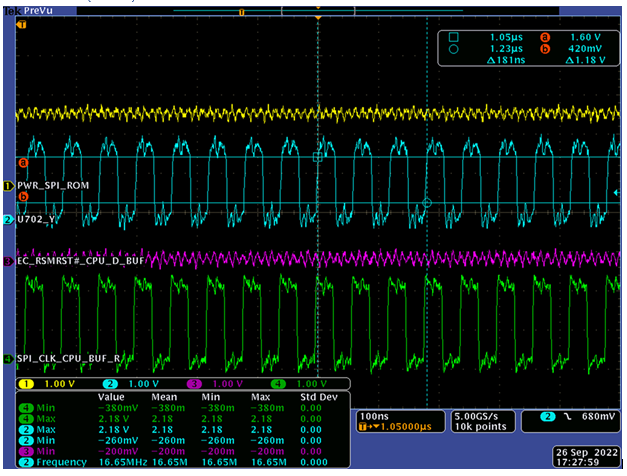

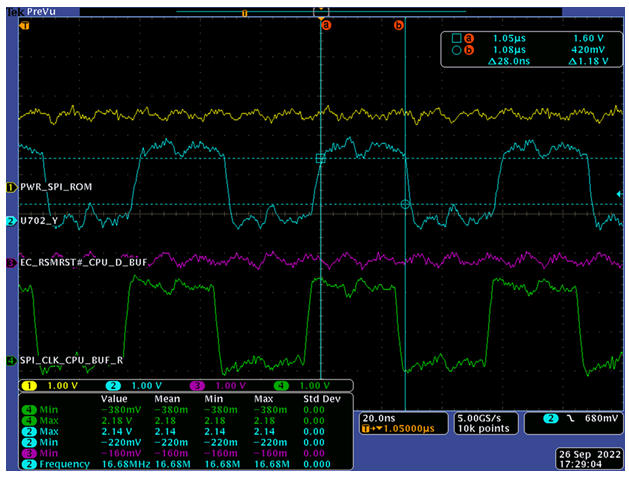

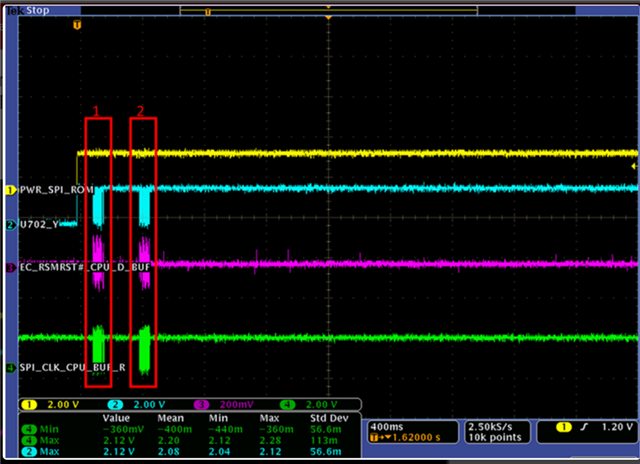

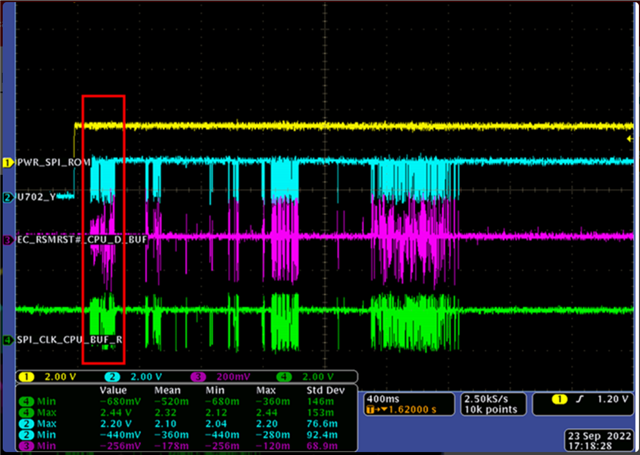

my customer found there's no clock signal when used our buffer,

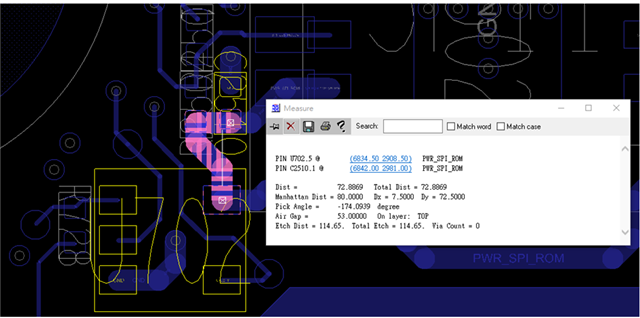

please noted that R735 is DY (the one below).

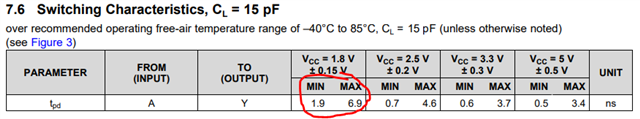

all signal level is 1.8V .

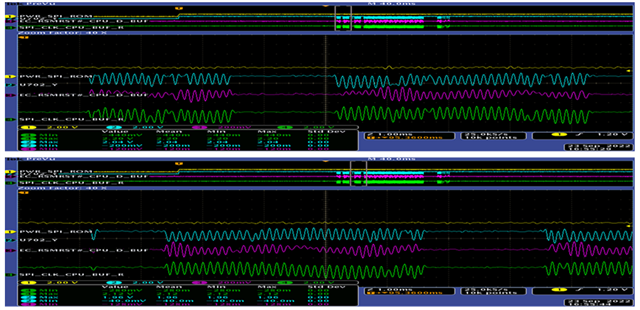

as you can see the blue and green are input and output , and they don't behave like a clock signal,

and they said the input signal is behaving normal without our buffer, also Nexperia p2p 74LVC1G125 doesn't have this problem.

please help check, thanks