Other Parts Discussed in Thread: TXV0106-Q1, SN74AUC34, TXV0108-Q1

Hi,

Does SN74AXCH8T245 suitable for below application?

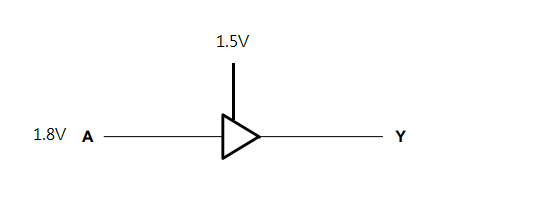

We need to use it for the signals on Ethernet MAC GMII. 1.5V to 1.8V (1.8V to 1.5V). The signals include:

- TX_CLK (125MHz), TXD0~D3 (4-bit RGMII signals), TX_CTL (Transmit control) → 1.5V to 1.8V (6 signals).

- RX_CLK (125MHz), RXD0~D3 (4-bit RGMII signals), RX_CTL (Receive control) → 1.8V to 1.5V (6 signals)

Thanks!

Jeff