Other Parts Discussed in Thread: TLV7021, TLV803E

Hello

I have a question about the output of 1G126.

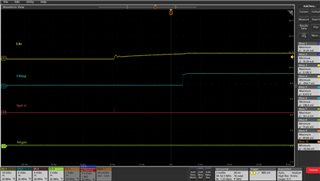

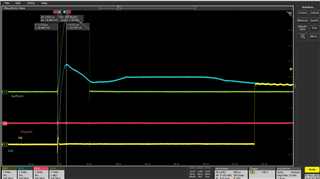

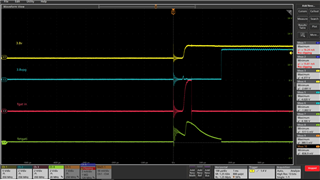

The yellow curve is the power supply of SN74LVC1G126. The blue curve is a reset signal of the power supply and it is connected to OE of the 1G126. The green curve is the output of the buffer.

The red curve is the input of 1G126, there is a pulse due to it is the output of a comparator(TLV7021). A pull up resistor connect the output of the comparator to power supply. Due to the POR of the comparator. The output of the comparator is high impedance during power on. As it is pull up to power supply, it is a high voltage level. But we do not expect a high voltage level at the output of the buffer due to the OE is low level and the output of the buffer is high impedance. Due to it is pull down with a 47kohm resistor. It should be low level. But we do see a high level at the output of the buffer.

During the test, we found it may linked with the ramp rate of the power supply. If the power supply established in more than 20us, the output is low during power on. But if the power supply established in less than 10us. It has a high level output. I would like to confirm with you about this behavior of 1G126. And could you provide a proper ramp rate for the buffer to work normally.

And if it is not linked to the ramp rate, please tell me why?

Thanks in advance!