Other Parts Discussed in Thread: TPS3422, SN74LVC1G123

Tool/software:

Hi ti team,

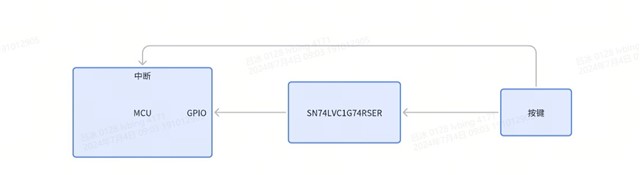

Please check the design of the latch. The requirement is that after triggering MCU to wake up, the low level state of the key press should be kept for about 1S, and then the GPIO of MCU will read it.

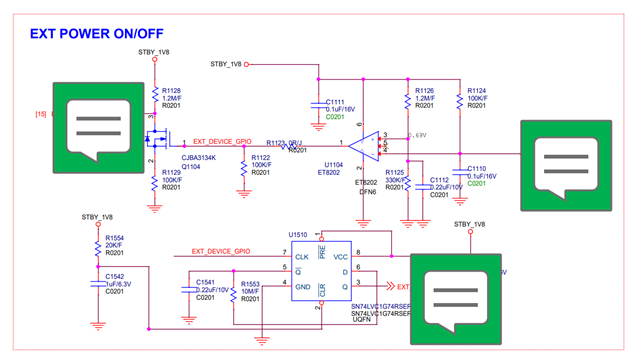

1. Help to check the peripheral schematic design of SN74LVC1G74RSER.

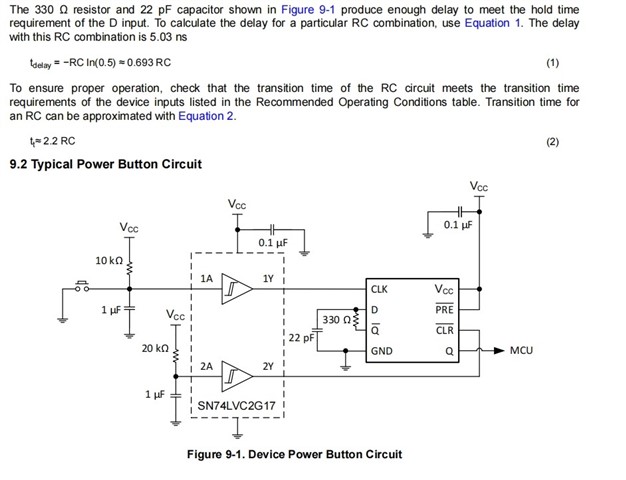

2. As shown in the following figure, which formula is used for the latching time?

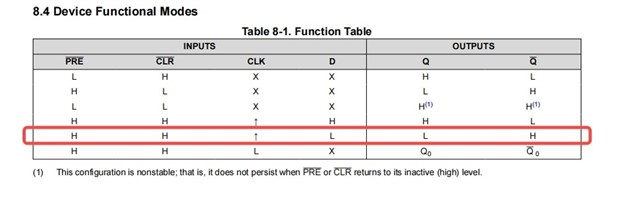

3. As shown in the figure below, both PRE and CLR are set high. When CLK detects the rising edge, Q outputs a low level, which is the result I want. (not added RC circuit); And then after latching 1S (according to RC), Q gets higher, right?