Tool/software:

Hello all,

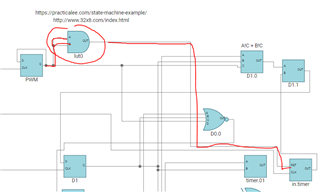

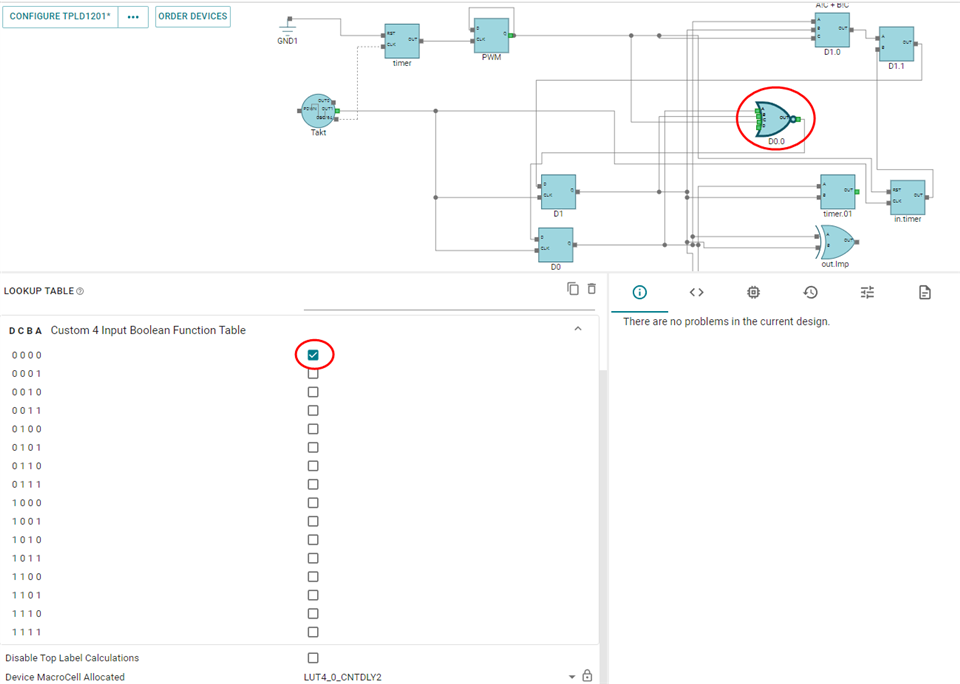

my customer wants to program our TPLD1201. He wants to use a logic gate with 4 inputs. With 4 tomes zero 0000 he wants to achieve on the output 1.

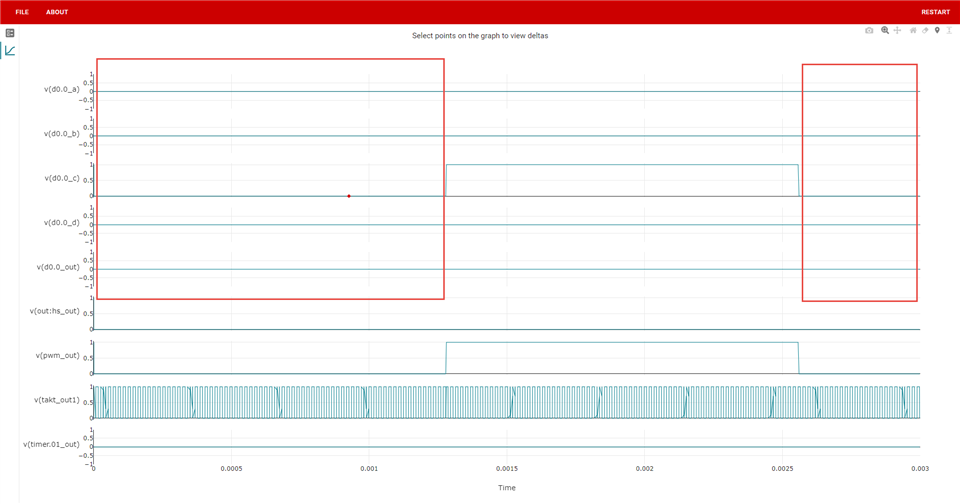

But on the simulation the customer gets a different result:

What is the reason for this? Attached the programming file:

statemachine_TI_Anfrage13082024.syscfg

Best regards

Olaf