Other Parts Discussed in Thread: SN74LVC1G08

Tool/software:

Hello Team,

I would have a follow up question to already closed question from this thread: https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1404713/sn74lvc1g32-q1-input-transition-rise-fall-time/5377355#5377355

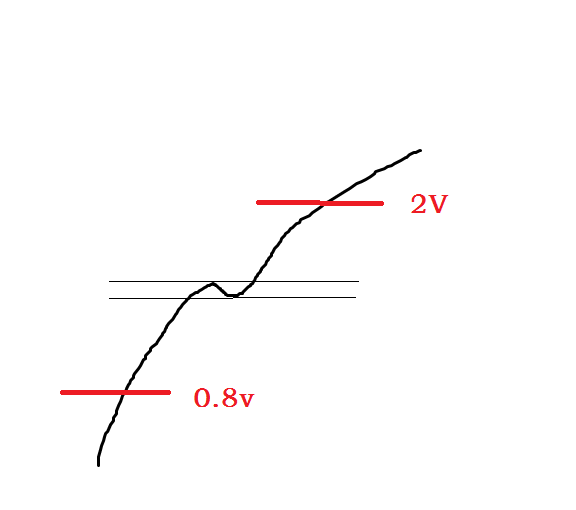

Assuming that we are looking at the transition from low to high, the data sheet shows that the gate detects a high level at the latest at 2 V input voltage on a 3.3 V supply (e.g. The SN74LVC1G08). So I understand that we need to make sure that we do not exceed the time of 33ns to reach the 2V threshold? After that, the behavior is irrelevant because the changeover has already taken place internally in the IC?

Thanks for your support and best regards,

Michael