Hi Adam,

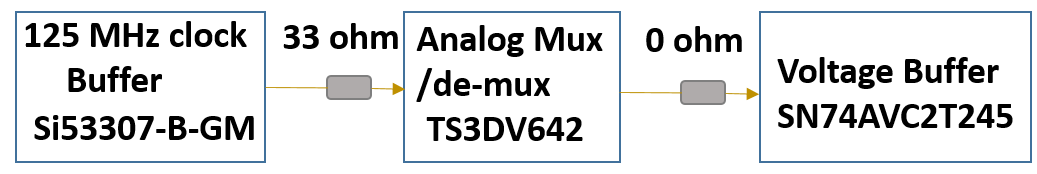

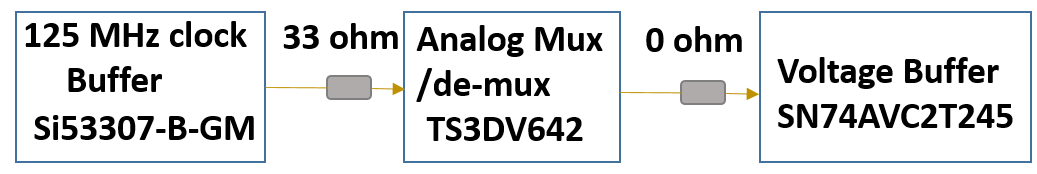

Iam using TS3DV642 as analog switch for RGMII signals. The analog mux is connected to a voltage level translator SN74AVC2T. The 125 MHz RGMII clock signal loses its monotonicity when it reaches the level translator.

Why is this happening between TS3DV642 D2- pin and voltage level translator ?

In the simulation when I put a series termination to this pin, the glitch is removed. Is it because of the impedance mismatch between D2- pin and voltage level translator?

Regards,

Bhavya